#### LECTURE NOTES

## EC3352-DIGITAL SYSTEM DESIGN

## II <u>YEAR - III SEMESTER - R2021</u> UNIT- I BASIC CONCEPTS

## **INTRODUCTION:**

In 1854, George Boole, an English mathematician, proposed algebra for symbolically representing problems in logic so that they may be analyzed mathematically. The mathematical systems founded upon the work of Boole are called *Boolean algebra* in his honor.

The application of a Boolean algebra to certain engineering problems was introduced in 1938 by C.E. Shannon.

For the formal definition of Boolean algebra, we shall employ the postulates formulated by E.V. Huntington in 1904.

#### **Fundamental postulates of Boolean algebra:**

The postulates of a mathematical system forms the basic assumption from which it is possible to deduce the theorems, laws and properties of the system.

The most common postulates used to formulate various structures are—

#### i) Closure:

A set S is closed w.r.t. a binary operator, if for every pair of elements of S, the binary operator specifies a rule for obtaining a unique element of S.

The result of each operation with operator (+) or (.) is either 1 or 0 and 1, 0 EB.

#### ii) Identity element:

A set S is said to have an identity element w.r.t a binary operation \* on S, if there exists an element e E S with the property,

Eg:

$$0+0=0$$

$0+1=1+0=1$  a)  $x+0=x$

$1.1=1$   $1.0=0.1=1$  b)  $x. 1=x$

#### iii) Commutative law:

A binary operator \* on a set S is said to be commutative if,

$$\mathbf{x} * \mathbf{y} = \mathbf{y} * \mathbf{x}$$

for all  $\mathbf{x}, \mathbf{y} \in \mathbf{S}$

**Eg:**

$$0+1=1+0=1$$

a)

$$x+y=y+x$$

$$0.1 = 1.0 = 0$$

b)

$$x. y= y. x$$

#### iv) Distributive law:

If \* and • are two binary operation on a set S, • is said to be distributive over + whenever,

$$x \cdot (y+z) = (x \cdot y) + (x \cdot z)$$

Similarly, + is said to be distributive over • whenever,

$$x + (y. z) = (x+ y). (x+ z)$$

## v) Inverse:

A set S having the identity element e, w.r.t. binary operator \* is said to have an inverse, whenever for every  $x \in S$ , there exists an element  $x' \in S$  such that,

a)

$$x + x' = 1$$

, since  $0 + 0' = 0 + 1$  and  $1 + 1' = 1 + 0 = 1$

b)

$$x. x' = 1$$

, since  $0.0' = 0.1$  and  $1.1' = 1.0 = 0$

#### **Summary:**

Postulates of Boolean algebra:

| POSTULATES                 | (a)                                                 | (b)                                                         |

|----------------------------|-----------------------------------------------------|-------------------------------------------------------------|

| Postulate 2 (Identity)     | $\mathbf{x} + 0 = \mathbf{x}$                       | $x \cdot 1 = x$                                             |

| Postulate 3 (Commutative)  | $\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$ | $\mathbf{x} \cdot \mathbf{y} = \mathbf{y} \cdot \mathbf{x}$ |

| Postulate 4 (Distributive) | x (y+z) = xy+xz                                     | x + yz = (x + y). (x + z)                                   |

| Postulate 5 (Inverse)      | x+x'=1                                              | $\mathbf{x.}\;\mathbf{x'}=0$                                |

## Basic theorem and properties of Boolean algebra:

#### **Basic Theorems:**

The theorems, like the postulates are listed in pairs; each relation is the dual of the one paired with it. The postulates are basic axioms of the algebraic structure and need no proof. The theorems must be proven from the postulates. The proofs of the theorems with one variable are presented below. At the right is listed the number of the postulate that justifies each step of the proof.

1) a)

$$x + x = x$$

$$x + x = (x + x) \cdot 1$$

by postulate  $2(b) [x \cdot 1 = x]$

$= (x + x) \cdot (x + x')$   $5(a) [x + x' = 1]$

$= x + xx'$   $4(b) [x + yz = (x + y)(x + z)]$

$= x + 0$   $5(b) [x \cdot x' = 0]$

$= x - 2(a) [x + 0 = x]$

b) x. x = x

$$x. x = (x. x) + 0$$

—by postulate 2(a) [x+ 0 = x]

$= (x. x) + (x. x')$ —5(b) [x. x' = 0]

$= x (x + x')$ —4(a) [x (y+z) = (xy)+ (xz)]

$= x (1)$ —5(a) [x+ x' = 1]

$= x$ —2(b) [x.1 = x]

2) a) x+1=1

b)

$$x \cdot 0 = 0$$

3)

$$(x')' = x$$

From postulate 5, we have x + x' = 1 and  $x \cdot x' = 0$ , which defines the complement of x. The complement of x' is x and is also (x')'.

Therefore, since the complement is unique,

$$(x')' = x.$$

### 4) Absorption Theorem:

a)

$$x + xy = x$$

$$x + xy = x$$

.  $1 + xy$ ——— by postulate 2(b) [x.  $1 = x$ ]

$= x (1 + y)$ ———  $4(a) [x (y + z) = (xy) + (xz)]$

$= x (1)$ —— by theorem 2(a) [x + 1 = x]

$= x$ — by postulate 2(a) [x.  $1 = x$ ]

b)

$$x. (x + y) = x$$

$x. (x + y) = x. x + x. y$   $4(a) [x (y + z) = (xy) + (xz)]$

$= x + x.y$  by theorem  $1(b)$   $[x. x = x]$

$= x.$  by theorem  $4(a)$   $[x + xy = x]$

c)

$$x + x'y = x + y$$

$x + x'y = x + xy + x'y - ...$  by theorem 4(a)  $[x + xy = x]$

$= x + y(x + x') - ...$  by postulate 4(a)  $[x(y+z) = (xy) + (xz)]$

$= x + y(1) - ...$  5(a)  $[x + x' = 1]$

$= x + y - ...$  2(b)  $[x. 1 = x]$

## Properties of Boolean algebra:

#### 1. Commutative property:

Boolean addition is commutative, given by

$$\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$$

According to this property, the order of the OR operation conducted on the variables makes no difference.

Boolean algebra is also commutative over multiplication given by,

$$\mathbf{x. y} = \mathbf{y. x}$$

This means that the order of the AND operation conducted on the variables makes no difference.

## 2. Associative property:

The associative property of addition is given by,

$$\mathbf{A} + (\mathbf{B} + \mathbf{C}) = (\mathbf{A} + \mathbf{B}) + \mathbf{C}$$

The OR operation of several variables results in the same, regardless of the grouping of the variables.

The associative law of multiplication is given by,

$$A. (B. C) = (A.B). C$$

It makes no difference in what order the variables are grouped during the AND operation of several variables.

#### 3. <u>Distributive property</u>:

The Boolean addition is distributive over Boolean multiplication, given by

$$A+BC = (A+B)(A+C)$$

The Boolean addition is distributive over Boolean addition, given by

$$A. (B+C) = (A.B)+ (A.C)$$

### 4. Duality:

It states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged.

If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

$$x+x'=1$$

is  $x. x'=0$

Duality is a very important property of Boolean algebra.

#### **Summary:**

Theorems of Boolean algebra:

|            | THEOREMS           | (a)                                    | (b)                                           |  |  |

|------------|--------------------|----------------------------------------|-----------------------------------------------|--|--|

|            | Idompotont         | $\mathbf{x} + \mathbf{x} = \mathbf{x}$ | $\mathbf{x} \cdot \mathbf{x} = \mathbf{x}$    |  |  |

| 1          | Idempotent         | x + 1 = 1                              | $\mathbf{x} \cdot 0 = 0$                      |  |  |

| 2          | Involution         | $(\mathbf{x}')' = \mathbf{x}$          |                                               |  |  |

| 3          | Alan a sunti a sa  | x + xy = x                             | x(x+y)=x                                      |  |  |

| Absorption | Absorption         | $x + x^2y = x + y$                     | $\mathbf{x.} \ (\mathbf{x'+y}) = \mathbf{xy}$ |  |  |

| 4          | Associative        | x+(y+z)=(x+y)+z                        | x (yz) = (xy) z                               |  |  |

| 5          | DeMorgan's Theorem | (x+y)'=x'.y'                           | (x. y)' = x' + y'                             |  |  |

#### **DeMorgan's Theorems:**

Two theorems that are an important part of Boolean algebra were proposed by DeMorgan.

The first theorem states that the complement of a product is equal to the sum of the complements.

$$(AB)' = A' + B'$$

The second theorem states that the complement of a sum is equal to the product of the complements.

$$(A+B)' = A'. B'$$

#### **Consensus Theorem:**

In simplification of Boolean expression, an expression of the form AB+ A'C+ BC, the term BC is redundant and can be eliminated to form the equivalent expression AB+ A'C. The theorem used for this simplification is known as consensus theorem and is stated as.

$$AB+A'C+BC=AB+A'C$$

The dual form of consensus theorem is stated as,

$$(A+B) (A'+C) (B+C) = (A+B) (A'+C)$$

## **BOOLEAN FUNCTIONS:**

## **Minimization of Boolean Expressions:**

The Boolean expressions can be simplified by applying properties, laws and theorems of Boolean algebra.

Simplify the following Boolean functions to a minimum number of literals:

1.

$$x (x'+y)$$

=  $xx'+xy$  [ $x. x'=0$ ]

=  $0+xy$  [ $x+0=x$ ]

2.

$$x+ x'y$$

=  $x + xy + x'y$  [  $x+ xy= x$ ]

=  $x+ y (x+x')$

=  $x+ y (1)$  [  $x+ x' = 1$ ]

=  $x+ y$ .

4.

$$xy + x'z + yz$$

.

=  $xy + x'z + yz(x + x')$  [  $x + x' = 1$ ]

=  $xy + x'z + xyz + x'yz$

Re-arranging,

$$= xy + xyz + x'z + x'yz$$

$$= xy (1+z) + x'z (1+y)$$

$$= xy + x'z.$$

[1+y=1]

5.

$$xy+yz+y'z$$

=  $xy+z(y+y')$

=  $xy+z(1)$

=  $xy+z$ . [  $y+y'=1$ ]

6.

$$(x+y) (x'+z) (y+z)$$

=  $(x+y) (x'+z)$  [ dual form of consensus theorem,

$(A+B) (A'+C) (B+C) = (A+B) (A'+C)$  ]

7.

$$x'y+xy+x'y'$$

=  $y(x'+x)+x'y'$

=  $y(1)+x'y'$

=  $y+x'y'$

=  $y+x'y'$

=  $y+x'y'$

[ $x+x'y=x+y'$ ]

8.

$$x + xy' + x'y$$

=  $x (1 + y') + x'y$

=  $x (1) + x'y$

=  $x + x'y$

=  $x + y$ . [1+  $x = 1$ ]

[ $x + x'y = x + y$ ]

Re- arranging,

= 1

10.

$$(x'+y)(x+y)$$

=  $x'.x+x'y+yx+y.y$

=  $0+x'y+xy+y$  [  $x.x'=0$ ]; [  $x.x=x$ ]

=  $y(x'+x+1)$

=  $y(1)$  [  $1+x=1$  ]

11.

$$xy+ xyz+ xy (w+ z)$$

=  $xy (1+z+w+z)$

= x'(y'+y) + xy'z'

22.

$$[(xy)'+x'+xy]'$$

=  $[x'+y'+x'+xy]'$

=  $[x'+y'+xy]'$   $[x+x=x]$

= yz+y'(z'+x)

= yz+ y'z'+ xy'

[x'+xy=x'+y]

$$= [x^{2} + y^{2} + x]^{2} \qquad [x^{2} + xy = x^{2} + y]$$

$$= [y^{2} + 1]^{2} \qquad [x + x^{2} = 1]$$

$$= 0.$$

$$23. [xy + xz]^{2} + x^{2}y^{2} \qquad = (xy)^{2}, (xz)^{2} + x^{2}y^{2} \qquad = (x^{2} + y^{2}), (x^{2} + x^{2})^{2} + x^{2}y^{2} \qquad = (x^{2} + y^{2}), (x^{2} + x^{2})^{2} + x^{2}y^{2} \qquad = x^{2} + x^{2} + x^{2} + x^{2} + x^{2}y^{2} + x^{2}y^{2} \qquad = x^{2} + x^{2} + x^{2} + x^{2}y^{2} + x^{2}y^{2} \qquad = x^{2} + x^{2} + x^{2}y^{2} + x^{2}y^{2} \qquad = x^{2} + x^{2}y^{2}$$

## **COMPLEMENT OF A FUNCTION:**

The complement of a function F is F' and is obtained from an interchange of o's for 1's and 1's for 0's in the value of F. The complement of a function may be derived algebraically through DeMorgan's theorem.

DeMorgan's theorems for any number of variables resemble in form the two-variable case and can be derived by successive substitutions similar to the method used in the preceding derivation. These theorems can be generalized as —

Find the complement of the following functions,

1.

$$F = x'yz' + x'y'z$$

$F' = (x'yz' + x'y'z)'$

$= (x'' + y' + z'') \cdot (x'' + y'' + z')$

$= (x + y' + z) \cdot (x + y + z').$

#### 2. F = (xy + y'z + xz) x.

## 3. F = x (y'z' + yz)

$$F' = [x (y'z' + yz)]'$$

$$= x' + (y'z' + yz)'$$

$$= x' + (y'z')'. (yz)'$$

$$= x' + (y'' + z''). (y' + z')$$

$$= x' + (y + z). (y' + z').$$

## 4. F = xy' + x'y

$$F' = (xy' + x'y)'$$

$$= (xy')'. (x'y)'$$

$$= (x'+y) (x+y')$$

$$= x'x + x'y' + yx + yy'$$

$$= x'y' + xy.$$

## 5. f = wx'y + xy' + wxz

## **CANONICAL AND STANDARD FORMS:**

#### **Minterms and Maxterms:**

A binary variable may appear either in its normal form (x) or in its complement form (x). Now either two binary variables x and y combined with an AND operation. Since each variable may appear in either form, there are four possible combinations:

Each of these four AND terms is called a 'minterm'.

In a similar fashion, when two binary variables x and y combined with an OR operation, there are four possible combinations:

$$x' + y', x' + y, x + y' \text{ and } x + y$$

Each of these four OR terms is called a 'maxterm'.

The minterms and maxterms of a 3- variable function can be represented as in table below.

| Variables |   | Minterms | Maxterms       |                      |

|-----------|---|----------|----------------|----------------------|

| X         | y | Z        | mi             | Mi                   |

| 0         | 0 | 0        | $x'y'z' = m_0$ | $x+y+z=M_0$          |

| О         | 0 | 1        | $x'y'z = m_1$  | $x+y+z'=M_1$         |

| О         | 1 | О        | $x'yz' = m_2$  | $x + y' + z = M_2$   |

| О         | 1 | 1        | $x'yz = m_3$   | $x + y' + z' = M_3$  |

| 1         | 0 | О        | $xy'z' = m_4$  | $x' + y + z = M_4$   |

| 1         | 0 | 1        | $xy'z = m_5$   | $x' + y + z' = M_5$  |

| 1         | 1 | О        | $xyz' = m_6$   | $x' + y' + z = M_6$  |

| 1         | 1 | 1        | $xyz = m_7$    | $x' + y' + z' = M_7$ |

#### **Sum of Minterm: (Sum of Products)**

The logical sum of two or more logical product terms is called sum of products expression. It is logically an OR operation of AND operated variables such as:

#### **Sum of Maxterm:** (Product of Sums)

A product of sums expression is a logical product of two or more logical sum terms. It is basically an AND operation of OR operated variables such as,

1.

$$Y = (A+B) \cdot (B+C) \cdot (A+C)$$

Product

Product

2.

$$Y = (A+B) \cdot (\overline{B}+C) \cdot (A+\overline{C})$$

#### **Canonical Sum of product expression:**

If each term in SOP form contains all the literals then the SOP is known as standard (or) canonical SOP form. Each individual term in standard SOP form is called minterm canonical form.

$$F(A, B, C) = AB'C + ABC + ABC'$$

#### Steps to convert general SOP to standard SOP form:

- 1. Find the missing literals in each product term if any.

- 2. AND each product term having missing literals by ORing the literal and its complement.

- 3. Expand the term by applying distributive law and reorder the literals in the product term.

- 4. Reduce the expression by omitting repeated product terms if any.

Obtain the canonical SOP form of the function:

$$= \sum m (4, 5, 6, 7).$$

3.  $Y(A,B,C)=A+BC$

$$= A. (B+B'). (C+C')+(A+A'). BC$$

$$= (AB+AB'). (C+C')+ABC+A'BC$$

$$= \underline{ABC}+ABC'+AB'C+AB'C'+\underline{ABC}+A'BC$$

$$= ABC+ABC'+AB'C+AB'C'+A'BC$$

$$= m_7+m_6+m_5+m_4+m_3$$

$$= \sum m (3, 4, 5, 6, 7).$$

4.

$$Y (A, B, C) = AC + AB + BC$$

$= AC (B + B') + AB (C + C') + BC (A + A')$

$= ABC + AB'C + ABC + ABC' + ABC + A'BC$

$= ABC + AB'C + ABC' + A'BC$

$= \sum m (3, 5, 6, 7).$

#### **Canonical Product of sum expression:**

If each term in POS form contains all literals then the POS is known as standard (or) Canonical POS form. Each individual term in standard POS form is called Maxterm canonical form.

- F(A, B, C) = (A + B + C). (A + B' + C). (A + B + C')

- F(x, y, z) = (x + y' + z'). (x' + y + z). (x + y + z)

## Steps to convert general POS to standard POS form:

- 1. Find the missing literals in each sum term if any.

- 2. OR each sum term having missing literals by ANDing the literal and its complement.

- 3. Expand the term by applying distributive law and reorder the literals in the sum term.

- 4. Reduce the expression by omitting repeated sum terms if any.

Obtain the canonical POS expression of the functions:

```

1. Y = A + B'C

= (A + B') (A + C)

[A+BC=(A+B)(A+C)]

= (A + B' + C.C') (A + C + B.B')

= (A + B' + C) (A + B' + C') (A + B + C) (A + B' + C)

= (A + B' + C). (A + B' + C'). (A + B + C)

= M_2, M_3, M_0

= \prod M(0, 2, 3)

2. Y = (A+B)(B+C)(A+C)

= (A+B+C.C') (B+C+A.A') (A+C+B.B')

= (A+B+C)(A+B+C')(A+B+C)(A'+B+C)(A+B+C)(A+B'+C)

= (A+B+C) (A+B+C') (A'+B+C) (A+B'+C)

= M_0. M_1. M_4. M_2

= \prod M(0, 1, 2, 4)

3. Y = A. (B + C + A)

= (A + B.B' + C.C'). (A + B + C)

= (A+B+C) (A+B+C') (A+B'+C) (A+B'+C') (A+B+C)

= (A+B+C) (A+B+C') (A+B'+C) (A+B'+C')

= M_0. M_1. M_2. M_3

= \prod M(0, 1, 2, 3)

4. Y = (A+B')(B+C)(A+C')

= (A+B'+C.C') (B+C+A.A') (A+C'+B.B')

= (A+B'+C) (A+B'+C') (A+B+C) (A'+B+C) (A+B+C') (A+B'+C')

= (A+B'+C) (A+B'+C') (A+B+C) (A'+B+C) (A+B+C')

= M_2, M_3, M_0, M_4, M_1

= \prod M (0, 1, 2, 3, 4)

Y = xy + x'z

5.

= (xy+x')(xy+z)Using distributive law, convert the function into OR terms.

= (x+x') (y+x') (x+z) (y+z)

[x+x'=1]

= (x'+y)(x+z)(y+z)

= (x'+y+z.z')(x+z+y.y')(y+z+x.x')

= (x'+v+z)(x'+v+z')(x+v+z)(x+v+z)(x+v+z)(x'+v+z)

```

= (x'+y+z)(x'+y+z')(x+y+z)(x+y'+z)

- $= M_4. M_5. M_0.M_2$

- $= \prod M (0, 2, 4, 5).$

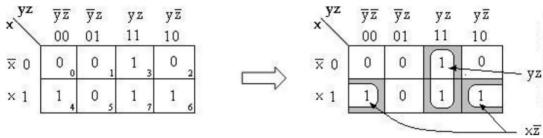

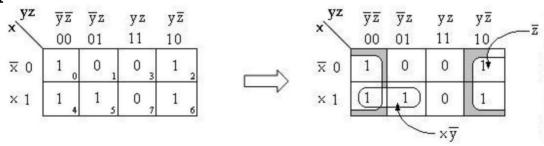

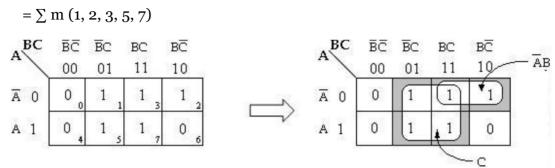

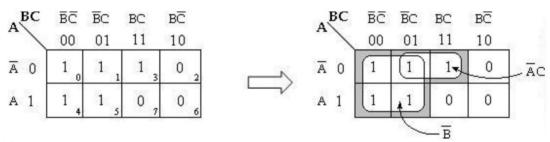

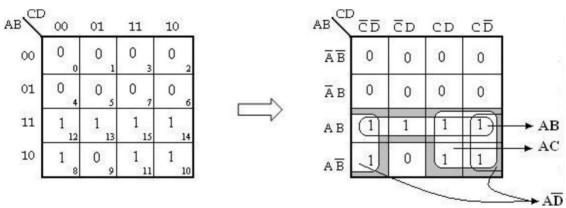

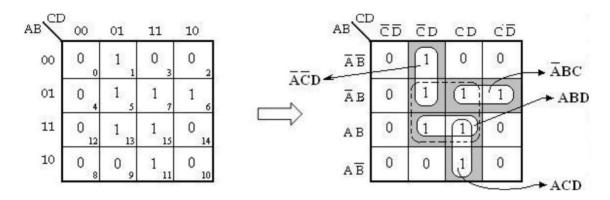

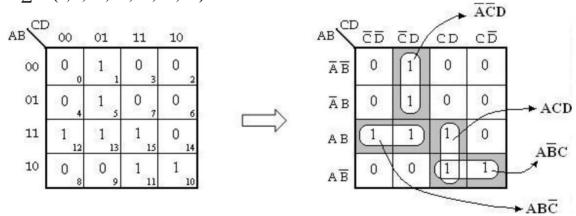

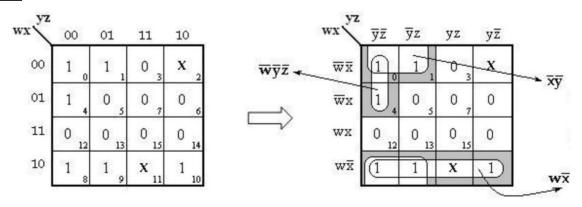

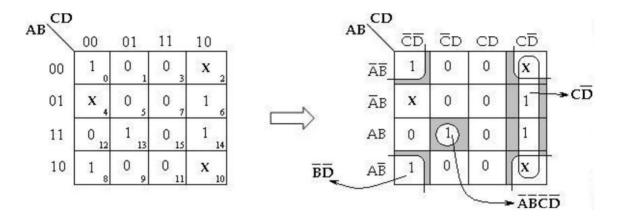

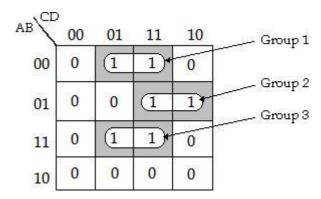

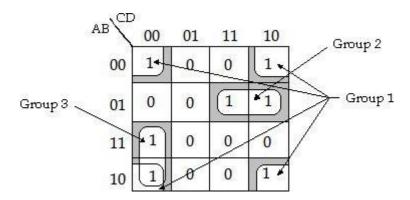

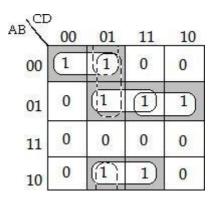

#### KARNAUGH MAP MINIMIZATION:

The simplification of the functions using Boolean laws and theorems becomes complex with the increase in the number of variables and terms. The map method, first proposed by Veitch and slightly improvised by Karnaugh, provides a simple, straightforward procedure for the simplification of Boolean functions. The method is called **Veitch diagram** or **Karnaugh map**, which may be regarded as a pictorial representation of a truth table.

The Karnaugh map technique provides a systematic method for simplifying and manipulation of Boolean expressions. A K-map is a diagram made up of squares, with each square representing one minterm of the function that is to be minimized. For n variables on a Karnaugh map there are 2n numbers of squares. Each square or cell represents one of the minterms. It can be drawn directly from either minterm (sum-of-products) or maxterm (product-of-sums) Boolean expressions.

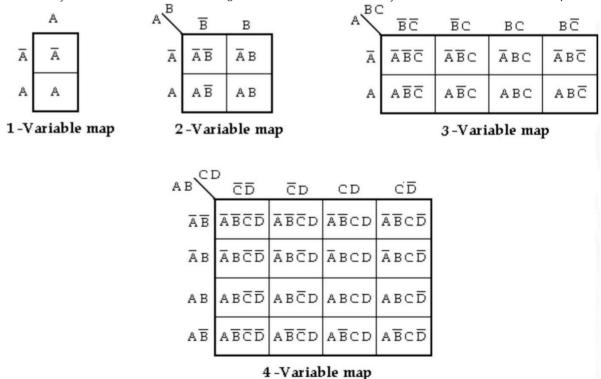

#### Two- Variable, Three Variable and Four Variable Maps

Karnaugh maps can be used for expressions with two, three, four and five variables. The number of cells in a Karnaugh map is equal to the total number of possible input variable combinations as is the number of rows in a truth table. For three variables, the number of cells is  $2_3 = 8$ . For four variables, the number of cells is  $2_4 = 16$ .

Product terms are assigned to the cells of a K-map by labeling each row and each column of a map with a variable, with its complement or with a combination of variables & complements. The below figure shows the way to label the rows & columns of a 1, 2, 3 and 4- variable maps and the product terms corresponding to each cell.

It is important to note that when we move from one cell to the next along any row or from one cell to the next along any column, one and only one variable in the product term changes (to a complement or to an uncomplemented form). Irrespective of number of variables the labels along each row and column must conform to a single change. Hence gray code is used to label the rows and columns of K-map as shown ow.

m12

$m_8$

11

10

m13

m9

m15

m11

m14

$m_{10}$

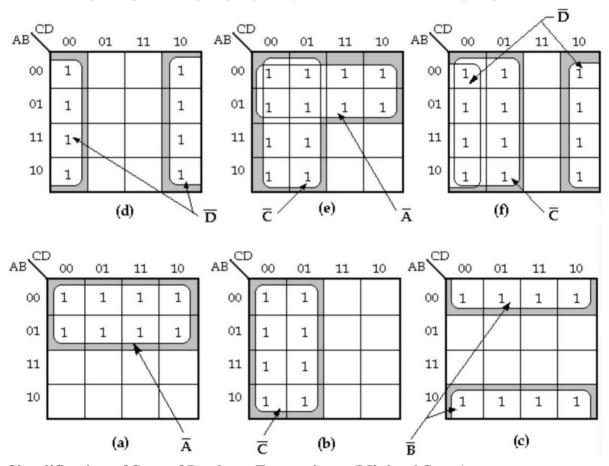

**Grouping cells for Simplification:**

The grouping is nothing but combining terms in adjacent cells. The simplification is achieved by grouping adjacent 1's or 0's in groups of 2i, where i = 1, 2, ..., n and n is the number of variables. When adjacent 1's are grouped then we get result in the sum of product form; otherwise we get result in the product of sum form.

4- Variable map

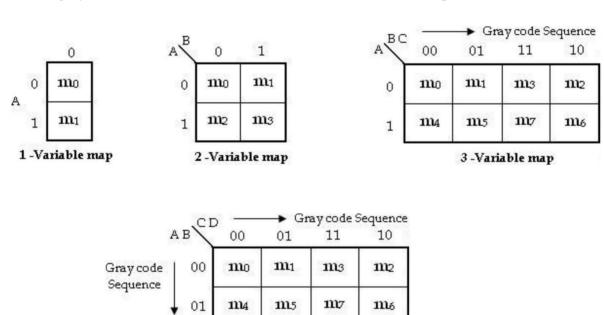

## Grouping Two Adjacent 1's: (Pair)

In a Karnaugh map we can group two adjacent 1's. The resultant group is called Pair.

**Examples of Pairs**

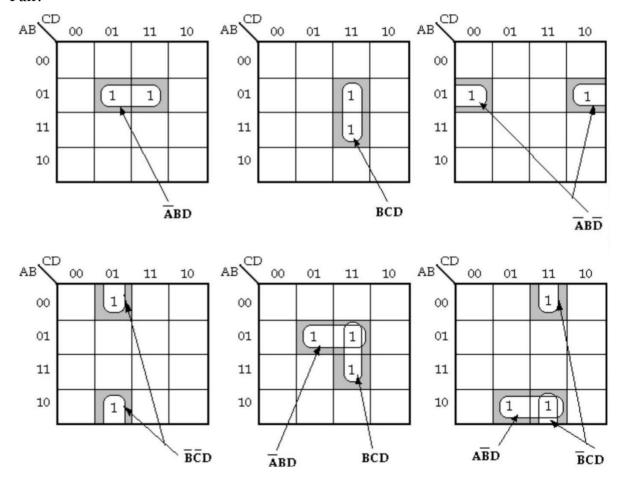

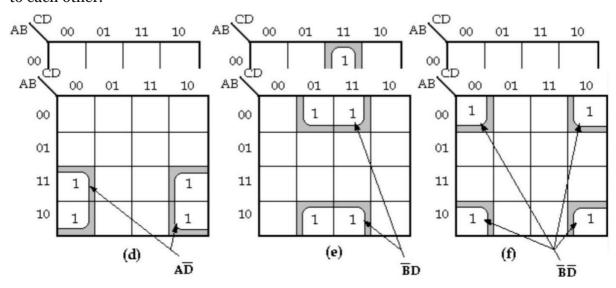

## Grouping Four Adjacent 1's: (Quad)

In a Karnaugh map we can group four adjacent 1's. The resultant group is called Quad. Fig (a) shows the four 1's are horizontally adjacent and Fig (b) shows they are vertically adjacent. Fig (c) contains four 1's in a square, and they are considered adjacent to each other.

#### **Examples of Quads**

The four 1's in fig (d) and fig (e) are also adjacent, as are those in fig (f) because, the top and bottom rows are considered to be adjacent to each other and the leftmost and rightmost columns are also adjacent to each other.

## **Grouping Eight Adjacent 1's: (Octet)**

In a Karnaugh map we can group eight adjacent 1's. The resultant group is called Octet.

Simplification of Sum of Products Expressions: (Minimal Sums)

The generalized procedure to simplify Boolean expressions as follows:

- 1. Plot the K-map and place 1's in those cells corresponding to the 1's in the sum of product expression. Place 0's in the other cells.

- 2. Check the K-map for adjacent 1's and encircle those 1's which are not adjacent to any other 1's. These are called **isolated 1's**.

- 3. Check for those 1's which are adjacent to only one other 1 and encircle such pairs.

- 4. Check for **quads** and **octets** of adjacent 1's even if it contains some 1's that have already been encircled. While doing this make sure that there are minimum number of groups.

- 5. Combine any pairs necessary to include any 1's that have not yet been grouped.

- 6. Form the simplified expression by summing product terms of all the groups.

## Three- Variable Map:

1. Simplify the Boolean expression,

$$F(x, y, z) = \sum m (3, 4, 6, 7).$$

#### Soln:

$$\mathbf{F} = \mathbf{y}\mathbf{z} + \mathbf{x}\mathbf{z}'$$

2.  $F(x, y, z) = \sum m(0, 2, 4, 5, 6)$ .

#### Soln:

$$F = z' + xy'$$

3. F=A'C+A'B+AB'C+BC

#### Soln:

$$= A'C (B+B') + A'B (C+C') + AB'C + BC (A+A')$$

$$= \underline{A'BC} + \underline{A'B'C} + \underline{A'BC} + \underline{A'BC} + \underline{AB'C} + \underline{ABC} + \underline{A'BC}$$

$$=$$

A'BC+ A'B'C + A'BC' + AB'C + ABC

$= m_3 + m_1 + m_2 + m_5 + m_7$

F=C+A'B

# **4.** AB'C + A'B'C + A'BC + AB'C' + A'B'C' Soln:

=

$$m5 + m1 + m3 + m4 + m0$$

=  $\sum m (0, 1, 3, 4, 5)$

F=A'C+B'

Soln:

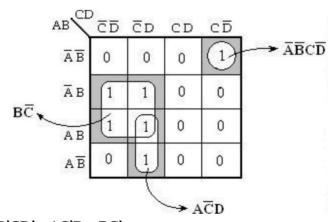

## Four - Variable Map:

1. Simplify the Boolean expression,

$$Y = A'BC'D' + A'BC'D + ABC'D' + ABC'D + AB'C'D + A'B'CD'$$

Therefore, Y = A'B'CD' + AC'D + BC'

# 2. F (w, x, y, z) = $\sum$ m(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14) Soln:

Therefore,

$$F = y' + w'z' + xz'$$

- 3. F= A'B'C'+ B'CD'+ A'BCD'+ AB'C'

- = A'B'C'(D+D') + B'CD'(A+A') + A'BCD' + AB'C'(D+D')

- = A'B'C'D+ A'B'C'D'+ AB'CD'+ A'B'CD'+ A'BCD'+ AB'C'D+ AB'C'D'

- $= m_1 + m_0 + m_{10} + m_2 + m_6 + m_9 + m_8$

- $= \sum m (0, 1, 2, 6, 8, 9, 10)$

Therefore,

F= B'D'+ B'C'+ A'CD'.

#### 4. Y = ABCD + AB'C'D' + AB'C + AB

- = ABCD + AB'C'D' + AB'C(D+D') + AB(C+C')(D+D')

- = ABCD+ AB'C'D'+ AB'CD+ AB'CD'+ (ABC+ ABC') (D+ D')

- = <u>ABCD</u>+ AB'C'D'+ AB'CD+ AB'CD'+ <u>ABCD</u>+ ABCD'+ ABC'D+ ABC'D'

- = ABCD+ AB'C'D'+ AB'CD+ AB'CD'+ ABCD'+ ABC'D+ ABC'D'

- $= m_{15} + m_{8} + m_{11} + m_{10} + m_{14} + m_{13} + m_{12}$

- $= \sum m (8, 10, 11, 12, 13, 14, 15)$

Therefore,

Y = AB + AC + AD'.

Therefore,

Y = AB + AC + AD + BCD.

6. Y= A'B'C'D+ A'BC'D+ A'BCD+ A'BCD'+ ABC'D+ ABCD+ AB'CD

=

$$m_1$$

+  $m_5$ +  $m_7$ +  $m_6$ +  $m_{13}$ +  $m_{15}$ +  $m_{11}$

=  $\sum \mathbf{m} (1, 5, 6, 7, 11, 13, 15)$

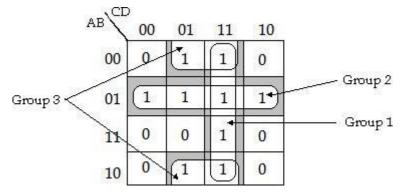

In the above K-map, the cells 5, 7, 13 and 15 can be grouped to form a quad as indicated by the dotted lines. In order to group the remaining 1's, four pairs have to be formed. However, all the four 1's covered by the quad are also covered by the pairs. So, the quad in the above k-map is redundant.

Therefore, the simplified expression will be,

$$Y = A'C'D + A'BC + ABD + ACD.$$

## 7. $Y = \sum m (1, 5, 10, 11, 12, 13, 15)$

Therefore, Y= A'C'D+ ABC'+ ACD+ AB'C.

Therefore, Y = AD' + B'C + B'D'

## 9. $F(A, B, C, D) = \sum_{i=1}^{n} m(0, 1, 4, 8, 9, 10)$

Therefore, F = A'C'D' + AB'D' + B'C'.

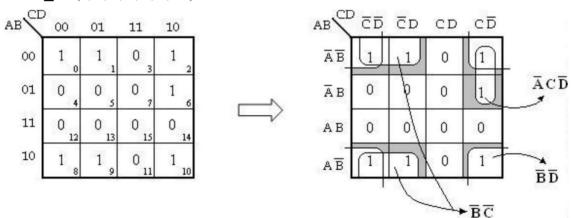

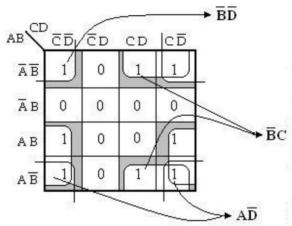

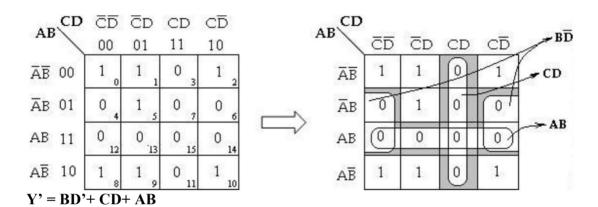

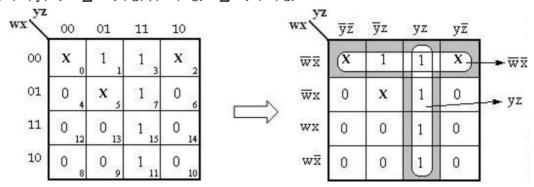

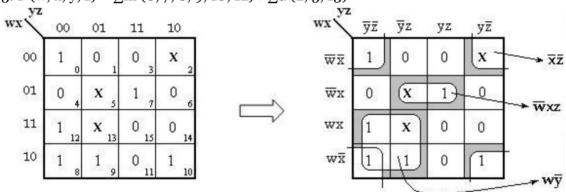

## **Simplification of Sum of Products Expressions: (Minimal Sums)**

$$Y' = B'C' + A'C + BC.$$

$$Y=Y" = (B'C' + A'C + BC)'$$

$$= (B'C')'. (A'C)'. (BC)'$$

$$= (B" + C"). (A" + C'). (B' + C')$$

$$Y = (B + C). (A + C'). (B' + C')$$

- $= M_{12}$ .  $M_{14}$ .  $M_{15}$ .  $M_{8}$ .  $M_{6}$ .  $M_{7}$ .  $M_{0}$ .  $M_{13}$

- $= \prod M (0, 6, 7, 8, 12, 13, 14, 15)$

| $AB \setminus CD$ | ΖD  | $\overline{\mathbb{C}}\mathbb{D}$ | CD   | $C\overline{\mathbb{D}}$ |

|-------------------|-----|-----------------------------------|------|--------------------------|

| Ab                | 00  | 01                                | 11   | 10                       |

| Ā <u>B</u> 00     | 0 0 | 1 1                               | 1 3  | 1 2                      |

| ĀB 01             | 1 4 | 1 5                               | 0 7  | 0 6                      |

| AB 11             | 0   | 0 13                              | 0 15 | 0                        |

| AB 10             | 0 8 | 1 ,                               | 1 11 | 1 10                     |

#### Y' = B'C'D' + AB + BC

Therefore, Y = (B + C + D). (A' + B'). (B' + C')

### 3. $F(A, B, C, D) = \prod M (0, 2, 3, 8, 9, 12, 13, 14, 15)$

| ABCD          | Ō̄   | ⊡D<br>01 | CD<br>11 | C̄̄̄̄̄̄<br>10 |

|---------------|------|----------|----------|---------------|

| Ā <u>B</u> 00 | 0 0  | 1 1      | 0 3      | 0 2           |

| ĀB 01         | 1 4  | 1 5      | 1 ,      | 1 6           |

| AB 11         | 0 12 | 0 13     | 0        | 1             |

| A <u>B</u> 10 | 0 8  | 0 ,      | 1 11     | 1 10          |

Y' = A'B'D' + A'B'C + ABD + AC'

4.

$$F(A, B, C, D) = \sum m (0, 1, 2, 5, 8, 9, 10)$$

=  $\prod M (3, 4, 6, 7, 11, 12, 13, 14, 15)$

Therefore, Y = (B' + D). (C'+ D'). (A'+ B')

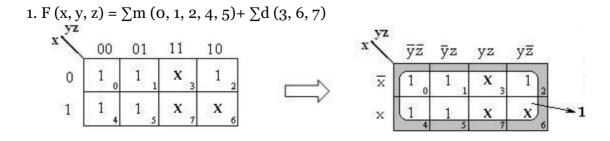

#### **Don't care Conditions:**

A don't care minterm is a combination of variables whose logical value is not specified. When choosing adjacent squares to simplify the function in a map, the don't care minterms may be assumed to be either 0 or 1. When simplifying the function, we can choose to include each don't care minterm with either the 1's or the 0's, depending on which combination gives the simplest expression.

$$F(x, y, z) = 1$$

2.  $F(w, x, y, z) = \sum m(1, 3, 7, 11, 15) + \sum d(0, 2, 5)$

F(w, x, y, z) = w'x' + yz

3.  $F(w, x, y, z) = \sum m(0, 7, 8, 9, 10, 12) + \sum d(2, 5, 13)$

F (w, x, y, z) = w'xz+ wy'+ x'z'. 4. F (w, x, y, z) =  $\sum$ m (0, 1, 4, 8, 9, 10)+  $\sum$ d (2, 11) Soln:

F(w, x, y, z) = wx' + x'y' + w'y'z'.

5.

$$F(A, B, C, D) = \sum m (0, 6, 8, 13, 14) + \sum d (2, 4, 10)$$

Soln:

F(A, B, C, D) = CD' + B'D' + A'B'C'D'.

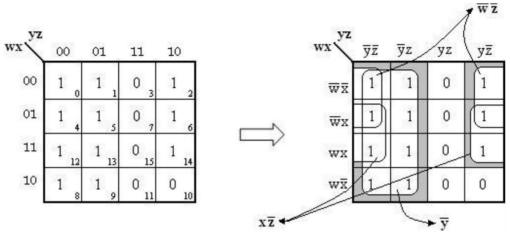

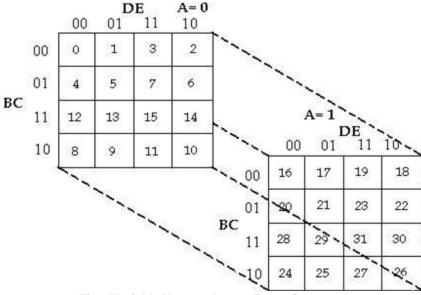

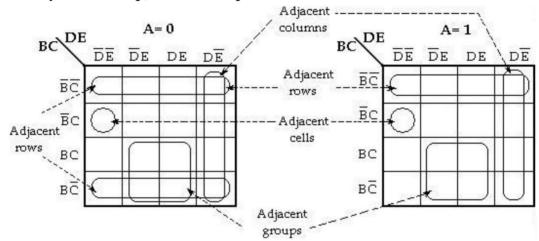

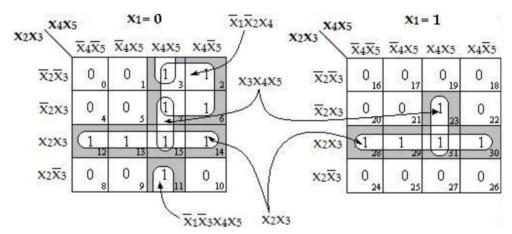

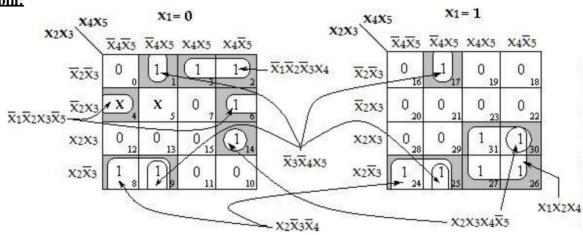

## **Five- Variable Maps:**

A 5- variable K- map requires 25= 32 cells, but adjacent cells are difficult to identify on a single 32-cell map. Therefore, two 16 cell K-maps are used.

If the variables are A, B, C, D and E, two identical 16- cell maps containing B, C, D and E can be constructed. One map is used for A and other for A'.

In order to identify the adjacent grouping in the 5- variable map, we must imagine the two maps superimposed on one another ie., every cell in one map is adjacent to the corresponding cell in the other map, because only one variable changes between such corresponding cells.

Five- Variable Karnaugh map (Layer Structure)

Thus, every row on one map is adjacent to the corresponding row (the one occupying the same position) on the other map, as are corresponding columns. Also, the rightmost and leftmost columns within each 16- cell map are adjacent, just as they are in any 16- cell map, as are the top and bottom rows.

Typical subcubes on a five-variable map

However, the rightmost column of the map is not adjacent to the leftmost column of the other map.

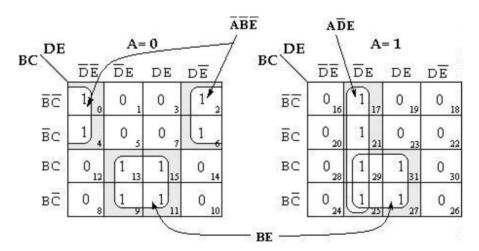

1. Simplify the Boolean function  $F(A, B, C, D, E) = \sum m (0, 2, 4, 6, 9, 11, 13, 15, 17, 21, 25, 27, 29, 31)$  Soln:

F(A, B, C, D, E) = A'B'E' + BE + AD'E

2.  $F(A, B, C, D, E) = \sum m(0, 5, 6, 8, 9, 10, 11, 16, 20, 24, 25, 26, 27, 29, 31)$  Soln:

F(A, B, C, D, E) = C'D'E' + A'B'CD'E + A'B'CDE' + AB'D'E' + ABE + BC'

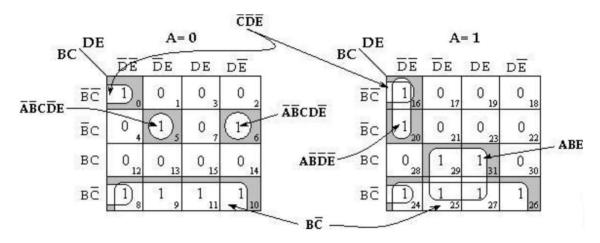

3. F (A, B, C, D, E) =  $\sum$ m (1, 4, 8, 10, 11, 20, 22, 24, 25, 26)+ $\sum$ d (0, 12, 16, 17) **Soln:**

F(A, B, C, D, E) = B'C'D' + A'D'E' + BC'E' + A'BC'D + AC'D' + AB'CE'

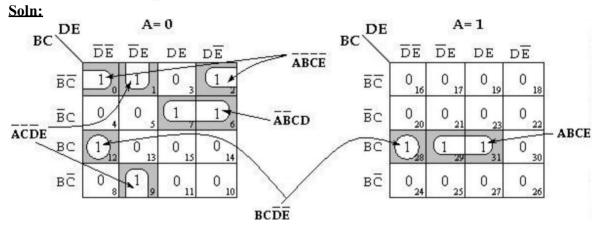

4.  $F(A, B, C, D, E) = \sum m(0, 1, 2, 6, 7, 9, 12, 28, 29, 31)$

F(A, B, C, D, E) = BCD'E' + ABCE + A'B'C'E' + A'C'D'E + A'B'CD

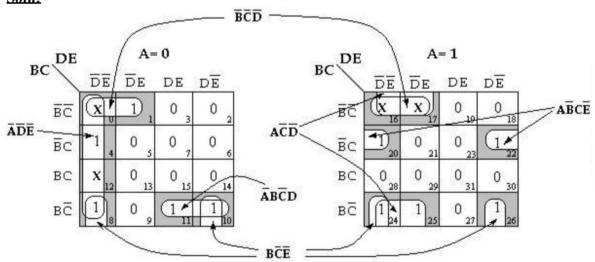

5.  $F(x_1, x_2, x_3, x_4, x_5) = \sum m(2, 3, 6, 7, 11, 12, 13, 14, 15, 23, 28, 29, 30, 31)$  **Soln:**

$F(x_1, x_2, x_3, x_4, x_5) = x_2x_3 + x_3x_4x_5 + x_1x_2x_4 + x_1x_3x_4x_5$

6. F (x<sub>1</sub>, x<sub>2</sub>, x<sub>3</sub>, x<sub>4</sub>, x<sub>5</sub>) =  $\sum$ m (1, 2, 3, 6, 8, 9, 14, 17, 24, 25, 26, 27, 30, 31)+  $\sum$ d (4, 5) **Soln:**

$F(x_1, x_2, x_3, x_4, x_5) = x_2x_3x_4x_4 + x_2x_3x_4x_5 + x_3x_4x_5 + x_1x_2x_4 + x_1x_2x_4 + x_1x_2x_3x_5 + x_1x_2x_4 + x_1x_2x_4 + x_1x_2x_3x_5 + x_1x_2x_5 + x_1x_5 +$

### **LOGIC GATES**

#### **BASIC LOGIC GATES:**

Logic gates are electronic circuits that can be used to implement the most elementary logic expressions, also known as Boolean expressions. The logic gate is the most basic building block of combinational logic.

There are three basic logic gates, namely the OR gate, the AND gate and the NOT gate. Other logic gates that are derived from these basic gates are the NAND gate, the NOR gate, the EXCLUSIVE- OR gate and the EXCLUSIVE-NOR gate.

| GATE              | SYMBOL                                                                                                | OPERATION                                                                                                                                          | TRUTH TABLE |                                                                                                       |             |                            |  |

|-------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------|-------------|----------------------------|--|

| <b>NOT</b> (7404) |                                                                                                       | NOT gate (Invertion), produces<br>an inverted output pulse for a<br>given input pulse.                                                             |             | $ \begin{array}{c cc} \mathbf{A} & \mathbf{Y} = \overline{\mathbf{A}} \\ 0 & 1 \\ 1 & 0 \end{array} $ |             |                            |  |

| AND<br>(7408)     | $ \begin{array}{c c} \underline{A} & & \underline{Y} \\ \underline{B} & & \underline{Y} \end{array} $ | AND gate performs logical multiplication. The output is HIGH only when all the inputs are HIGH. When any of the inputs are low, the output is LOW. |             | 0<br>0<br>1<br>1                                                                                      | 0<br>1<br>0 | Y= A.B<br>0<br>0<br>0<br>1 |  |

| OR<br>(7432)     |                                                                                                                                           | OR gate performs logical addition. It produces a HIGH on the output when any of the inputs are HIGH. The output is LOW only when all inputs are LOW. | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Y= A+B  0  1  1  1         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------------|

| NAND<br>(7400)   | $\underbrace{\frac{\mathbf{A}}{\mathbf{B}}}_{\mathbf{Y}=\overline{\mathbf{A}}.\overline{\mathbf{B}}}\underbrace{\mathbf{A}}_{\mathbf{B}}$ | It is a universal gate. When any of the inputs are LOW, the output will be HIGH. LOW output occurs only when all inputs are HIGH.                    | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Y= A.B  1 1 1 0            |

| NOR<br>(7402)    | $\underbrace{\frac{A}{B}}_{Y=\overline{A+B}} \underbrace{{A+B}}}_{Y}$                                                                     | It is a universal gate. LOW output occurs when any of its input is HIGH. When all its inputs are LOW, the output is HIGH.                            | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Y= A+B  1 0 0 0 0          |

| EX- OR<br>(7486) | $\underbrace{\frac{A}{B}}_{Y=A\oplus B}\underbrace{Y}$                                                                                    | The output is HIGH only when odd number of inputs is HIGH.                                                                                           | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Y= A⊕B<br>0<br>1<br>1<br>0 |

| EX- NOR          | $ \begin{array}{c} A \\ B \end{array} $ $ Y = \overline{A \oplus B} $ (or) $ Y = A \odot B $                                              | The output is HIGH only when even number of inputs is HIGH. Or when all inputs are zeros.                                                            | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Y= A⊙B<br>1<br>0<br>0<br>1 |

# **UNIVERSAL GATES:**

The NAND and NOR gates are known as universal gates, since any logic function can be implemented using NAND or NOR gates. This is illustrated in the following sections.

# a) NAND Gate:

The NAND gate can be used to generate the NOT function, the AND function,

the OR function and the NOR function.

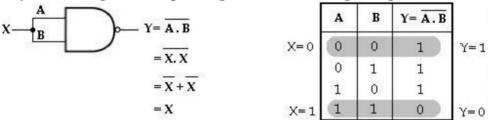

# i) NOT function:

By connecting all the inputs together and creating a single common input.

NOT function using NAND gate

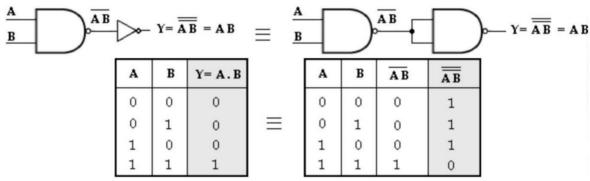

# ii) AND function:

By simply inverting output of the NAND gate. i.e.,

$$\overline{\overline{AB}} = AB$$

AND function using NAND gates

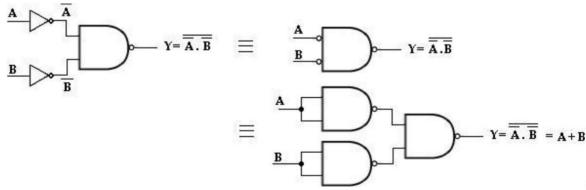

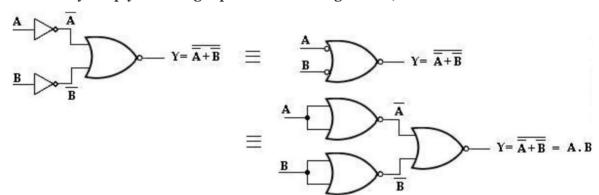

# iii) OR function:

By simply inverting inputs of the NAND gate. i.e.,

OR function using NAND gates

Bubble at the input of NAND gate indicates inverted input.

| Α | В | Y= A+B |          | A | В | Ā.B | $\overline{\overline{A}.\overline{B}}$ |

|---|---|--------|----------|---|---|-----|----------------------------------------|

| 0 | 0 | 0      |          | 0 | 0 | 1   | 0                                      |

| 0 | 1 | 1      | $\equiv$ | 0 | 1 | 0   | 1                                      |

| 1 | 0 | 1      |          | 1 | 0 | 0   | 1                                      |

| 1 | 1 | 1      |          | 1 | 1 | 0   | 1                                      |

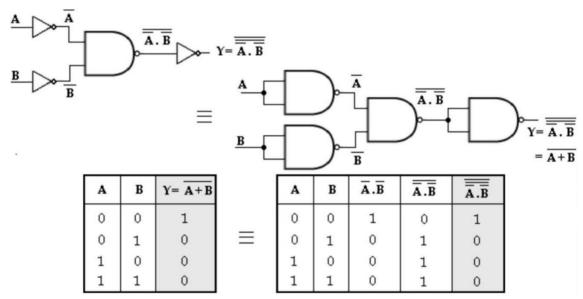

# iv) NOR function:

By inverting inputs and outputs of the NAND gate.

NOR function using NAND gates

# b) NOR Gate:

Similar to NAND gate, the NOR gate is also a universal gate, since it can be used to generate the NOT, AND, OR and NAND functions.

# i) NOT function:

By connecting all the inputs together and creating a single common input.

**NOT function using NOR gates**

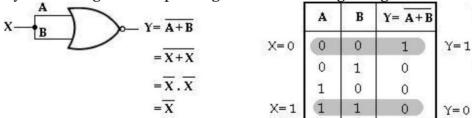

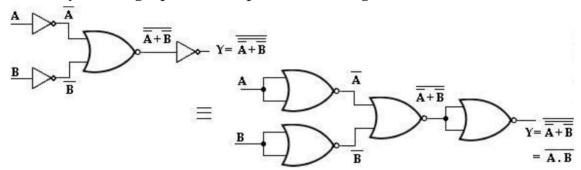

# ii) OR function:

By simply inverting output of the NOR gate. i.e.,

$$\overline{\overline{A+B}} = A+B$$

OR function using NOR gates

| A | В | Y= A+B |          |   |

|---|---|--------|----------|---|

| 0 | 0 | 0      |          | Г |

| 0 | 1 | 1      | $\equiv$ | l |

| 1 | 0 | 1      |          |   |

| 1 | 1 | 1      |          | l |

| A | В | A+B | A+B |  |  |

|---|---|-----|-----|--|--|

| 0 | 0 | 1   | 0   |  |  |

| 0 | 1 | 0   | 1   |  |  |

| 1 | 0 | 0   | 1   |  |  |

| 1 | 1 | 0   | 1   |  |  |

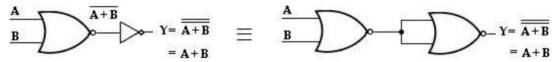

# iii) AND function:

By simply inverting inputs of the NOR gate. i.e.,

**AND function using NOR gates**

Bubble at the input of NOR gate indicates inverted input.

| A | В | Y= A.B |          | A | В | $\overline{A} + \overline{B}$ | $\overline{A} + \overline{B}$ |

|---|---|--------|----------|---|---|-------------------------------|-------------------------------|

| 0 | 0 | 0      |          | 0 | 0 | 1                             | 0                             |

| 0 | 1 | 0      | $\equiv$ | 0 | 1 | 1                             | 0                             |

| 1 | 0 | 0      |          | 1 | 0 | 1                             | 0                             |

| 1 | 1 | 1      |          | 1 | 1 | 0                             | 1                             |

Truth table

# iv) NAND Function:

By inverting inputs and outputs of the NOR gate.

NAND function using NOR gates

| A | В | $Y = \overline{A \cdot B}$ |          | A | В | $\overline{A} + \overline{B}$ | $\overline{A} + \overline{B}$ | $\overline{\overline{A} + \overline{B}}$ |

|---|---|----------------------------|----------|---|---|-------------------------------|-------------------------------|------------------------------------------|

| 0 | 0 | 1                          |          | 0 | 0 | 1                             | 0                             | 1                                        |

| 0 | 1 | 1                          | $\equiv$ | 0 | 1 | 1                             | 0                             | 1                                        |

| 1 | 0 | 1                          |          | 1 | 0 | 1                             | 0                             | 1                                        |

| 1 | 1 | 0                          |          | 1 | 1 | 0                             | 1                             | 0                                        |

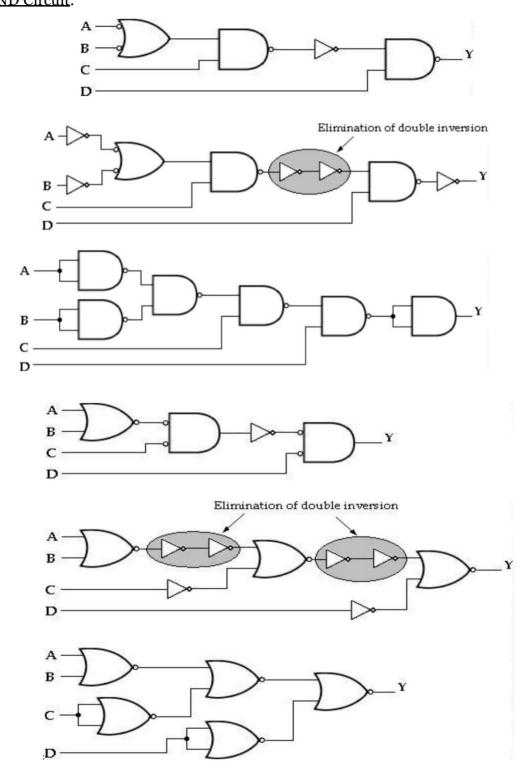

# Conversion of AND/OR/NOT to NAND/NOR:

- 1. Draw AND/OR logic.

- If NAND hardware has been chosen, add bubbles on the output of each AND gate and bubbles on input side to all OR gates.

If NOR hardware has been chosen, add bubbles on the output of each OR gate and bubbles on input side to all AND gates.

- 3. Add or subtract an inverter on each line that received a bubble in step 2.

- 4. Replace bubbled OR by NAND and bubbled AND by NOR.

- 5. Eliminate double inversions.

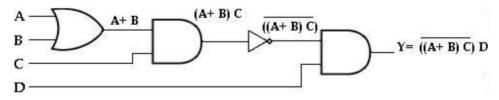

- 1. Implement Boolean expression using NAND gates:

$$(\overline{(A+B)C})D$$

# **Original Circuit:**

Soln: \_\_\_ NAND Circuit:

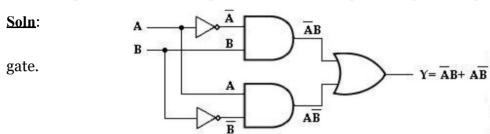

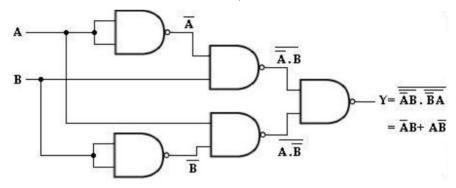

2. Implement Boolean expression for EX-OR gate using NAND gates.

Adding bubbles on the output of each AND gates and on the inputs of each OR

Adding an inverter on each line that received bubble,

Eliminating double inversion,

Replacing inverter and bubbled OR with NAND, we have

# UNIT II COMBINATIONAL LOGIC CIRCUITS:

### **Introduction:**

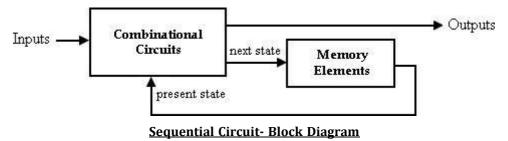

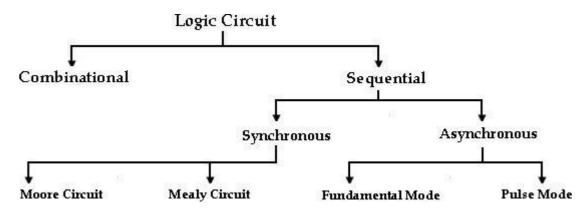

The digital system consists of two types of circuits, namely

- (i) Combinational circuits

- (ii) Sequential circuits

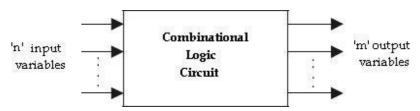

**Combinational circuit** consists of logic gates whose output at any time is determined from the present combination of inputs. The logic gate is the most basic building block of combinational logic. The logical function performed by a combinational circuit is fully defined by a set of Boolean expressions.

**Sequential logic circuit** comprises both logic gates and the state of storage elements such as flip-flops. As a consequence, the output of a sequential circuit depends not only on present value of inputs but also on the past state of inputs.

In the previous chapter, we have discussed binary numbers, codes, Boolean algebra and simplification of Boolean function and logic gates. In this chapter, formulation and analysis of various systematic designs of combinational circuits will be discussed.

A combinational circuit consists of input variables, logic gates, and output variables. The logic gates accept signals from inputs and output signals are generated according to the logic circuits employed in it. Binary information from the given data transforms to desired output data in this process. Both input and output are obviously the binary signals, *i.e.*, both the input and output signals are of two possible states, logic1 and logic 0.

Block diagram of a combinational logic circuit

For n number of input variables to a combinational circuit,  $2^n$  possible combinations of binary input states are possible. For each possible combination, there is one and only one possible output combination. A combinational logic circuit can be described by m Boolean functions and each output can be expressed in terms of n input variables.

#### **DESIGN PROCEDURE:**

Any combinational circuit can be designed by the following steps of design procedure.

- 1. The problem is stated.

- 2. Identify the input and output variables.

- 3. The input and output variables are assigned letter symbols.

- 4. Construction of a truth table to meet input -output requirements.

- 5. Writing Boolean expressions for various output variables in terms of input variables.

- 6. The simplified Boolean expression is obtained by any method of minimization—algebraic method, Karnaugh map method, or tabulation method.

- 7. A logic diagram is realized from the simplified boolean expression using logic gates.

The following guidelines should be followed while choosing the preferred form for hardware implementation:

- 1. The implementation should have the minimum number of gates, with the gates used having the minimum number of inputs.

- 2. There should be a minimum number of interconnections.

- 3. Limitation on the driving capability of the gates should not be ignored.

### ARITHMETIC CIRCUITS – BASIC BUILDING BLOCKS:

In this section, we will discuss those combinational logic building blocks that can be used to perform addition and subtraction operations on binary numbers. Addition and subtraction are the two most commonly used arithmetic operations, as the other two, namely multiplication and division, are respectively the processes of repeated addition and repeated subtraction.

The basic building blocks that form the basis of all hardware used to perform the arithmetic operations on binary numbers are half-adder, full adder, half-subtractor, full-subtractor.

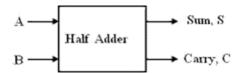

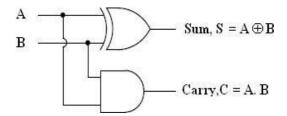

#### Half-Adder:

A half-adder is a combinational circuit that can be used to add two binary bits. It has two inputs that represent the two bits to be added and two outputs, with one producing the SUM output and the other producing the CARRY.

Block schematic of half-adder

The truth table of a half-adder, showing all possible input combinations and the corresponding outputs are shown below.

| Inp | outs | Outputs   |         |  |  |  |

|-----|------|-----------|---------|--|--|--|

| Α   | В    | Carry (C) | Sum (S) |  |  |  |

| 0   | 0    | 0         | 0       |  |  |  |

| 0   | 1    | 0         | 1       |  |  |  |

| 1   | 0    | 0         | 1       |  |  |  |

| 1   | 1    | 1         | 0       |  |  |  |

Truth table of half-adder

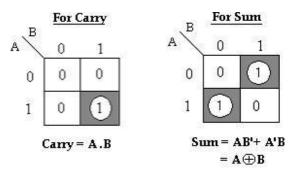

# K-map simplification for carry and sum:

The Boolean expressions for the SUM and CARRY outputs are given by the equations,

Sum,

$$S = A'B + AB' = A \square B$$

Carry,  $C = A . B$

The first one representing the SUM output is that of an EX-OR gate, the second one representing the CARRY output is that of an AND gate.

The logic diagram of the half adder is,

**Logic Implementation of Half-adder**

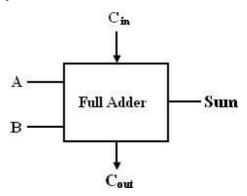

# Full-Adder:

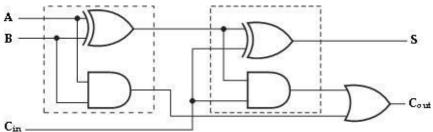

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of 3 inputs and 2 outputs.

Two of the input variables, represent the significant bits to be added. The third input represents the carry from previous lower significant position. The block diagram of full adder is given by,

**Block schematic of full-adder**

The full adder circuit overcomes the limitation of the half-adder, which can be used to add two bits only. As there are three input variables, eight different input combinations are possible. The truth table is shown below,

### **Truth Table:**

|   | Inputs |     | 0       | utputs       |

|---|--------|-----|---------|--------------|

| Α | В      | Cin | Sum (S) | Carry (Cout) |

| 0 | 0      | 0   | 0       | 0            |

| 0 | 0      | 1   | 1       | 0            |

| 0 | 1      | 0   | 1       | 0            |

| 0 | 1      | 1   | 0       | 1            |

| 1 | 0      | 0   | 1       | 0            |

| 1 | 0      | 1   | 0       | 1            |

| 1 | 1      | 0   | 0       | 1            |

| 1 | 1      | 1   | 1       | 1            |

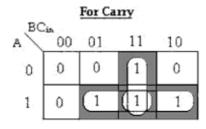

To derive the simplified Boolean expression from the truth table, the Karnaugh map method is adopted as,

Carry, Cout = AB+ ACin + BCin

Sum, S = A'B'Cin+ A'BC'in+ AB'C'in+ ABCin

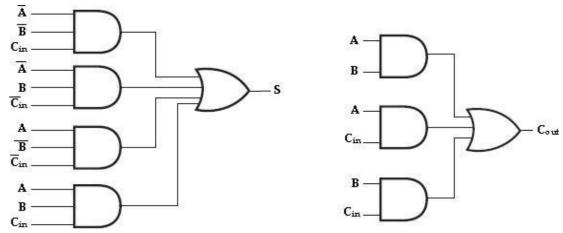

The Boolean expressions for the SUM and CARRY outputs are given by the equations,

The logic diagram for the above functions is shown as,

Implementation of full-adder in Sum of Products

The logic diagram of the full adder can also be implemented with two half-adders and one OR gate. The S output from the second half adder is the exclusive-OR of Cin and the output of the first half-adder, giving

Sum = C<sub>in</sub>

$$\Box$$

(A  $\Box$  B)

$$[x \Box y = x'y + xy']$$

$$= Cin  $\Box$  (A'B+AB') + C<sub>in</sub> (A'B+AB')'

$$[(x'y+xy')' = (xy+x'y')]$$

$$= C'in (A'B+AB') + Cin (AB+A'B')$$

$$= A'BC'in + AB'C'in + ABCin + A'B'Cin.$$$$

and the carry output is,

# Carry, Cout = AB+ Cin (A'B+AB')

$$= AB + A'BC_{in} + AB'C_{in}$$

$$= AB (C_{in}+1) + A'BC_{in} + AB'C_{in}$$

[C<sub>in</sub>+1=1]

$= ABC_{in} + AB + A'BC_{in} + AB'C_{in}$

$= AB + AC_{in} (B+B') + A'BC_{in}$

$= AB + AC_{in} + A'BC_{in}$

$$= AB (C_{in}+1) + AC_{in} + A'BC_{in}$$

[C<sub>in</sub>+1=1]

$= ABC_{in} + AB + AC_{in} + A'BC_{in}$

$= AB + AC_{in} + BC_{in} (A + A')$

$= AB + AC_{in} + BC_{in}$ .

Implementation of full adder with two half-adders and an OR gate

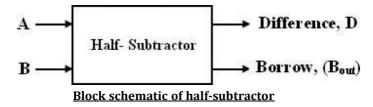

### **Half** -Subtractor:

A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output. The BORROW output here specifies whether a \_1' has been borrowed to perform the subtraction.

The truth table of half-subtractor, showing all possible input combinations and the corresponding outputs are shown below.

| In | put | Outp           | ut            |  |  |

|----|-----|----------------|---------------|--|--|

| A  | В   | Difference (D) | Borrow (Bout) |  |  |

| 0  | 0   | 0              | 0             |  |  |

| 0  | 1   | 1              | 1             |  |  |

| 1  | 0   | 1              | 0             |  |  |

| 1  | 1   | 0              | 0             |  |  |

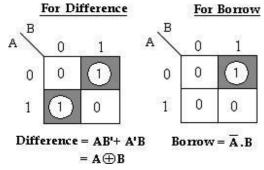

K-map simplification for half subtractor:

The Boolean expressions for the DIFFERENCE and BORROW outputs are given by the equations,

Difference, D =

$$A'B + AB' = A \square B$$

Borrow,  $B_{out}$  =  $A' \cdot B$

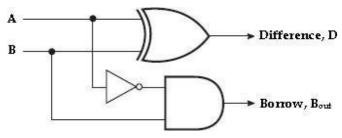

The first one representing the DIFFERENCE ( $\mathbf{D}$ )output is that of an exclusive-OR gate, the expression for the BORROW output ( $\mathbf{B}_{out}$ ) is that of an AND gate with input A complemented before it is fed to the gate.

The logic diagram of the half adder is,

**Logic Implementation of Half-Subtractor**

Comparing a half-subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs are just the same. The expression for BORROW in the case of the half-subtractor is also similar to what we have for CARRY in the case of the half-adder. If the input A, ie., the minuend is complemented, an AND gate can be used to implement the BORROW output.

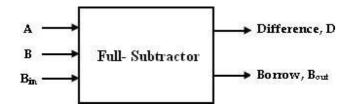

# **Full Subtractor:**

A *full subtractor* performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a \_1' has already been borrowed by the previous adjacent lower minuend bit or not.

As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as B<sub>in</sub>. There are two outputs, namely the DIFFERENCE output D and the BORROW output B<sub>o</sub>. The

BORROW output bit tells whether the minuend bit needs to borrow a \_1' from the next possible higher minuend bit.

#### **Block schematic of full-adder**

The truth table for full-subtractor is,

|   | Inputs |     | Outputs       |              |  |  |  |

|---|--------|-----|---------------|--------------|--|--|--|

| A | В      | Bin | Difference(D) | Borrow(Bout) |  |  |  |

| 0 | 0      | 0   | 0             | 0            |  |  |  |

| 0 | 0      | 1   | 1             | 1            |  |  |  |

| 0 | 1      | 0   | 1             | 1            |  |  |  |

| 0 | 1      | 1   | 0             | 1            |  |  |  |

| 1 | 0      | 0   | 1             | 0            |  |  |  |

| 1 | 0      | 1   | 0             | 0            |  |  |  |

| 1 | 1      | 0   | 0             | 0            |  |  |  |

| 1 | 1      | 1   | 1             | 1            |  |  |  |

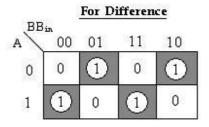

# K-map simplification for full-subtractor:

Difference,  $D = A'B'B_{in} + A'BB'_{in} + AB'B'_{in} + ABB_{in}$

Borrow,  $B_{out} = A'B + A'B_{in} + BB_{in}$

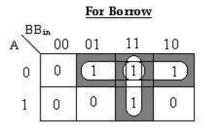

The Boolean expressions for the DIFFERENCE and BORROW outputs are given by the equations,

Difference, D = A'B'Bin+ A'BB'in + AB'B'in + ABBin

Borrow, Bout =  $A'B+ A'C_{in} + BB_{in}$ .

The logic diagram for the above functions is shown as,

#### Implementation of full-adder in Sum of Products

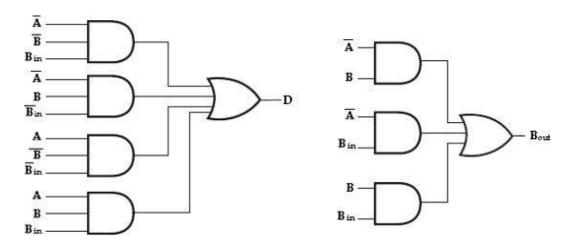

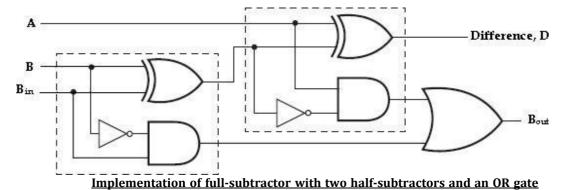

The logic diagram of the full-subtractor can also be implemented with two half-subtractors and one OR gate. The difference,D output from the second half subtractor is the exclusive-OR of B<sub>in</sub> and the output of the first half-subtractor, giving

. and the borrow output is,

# Therefore,

we can implement full-subtractor using two half-subtractors and OR gate as,

# **Binary Adder (Parallel Adder):**

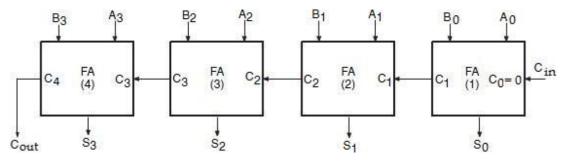

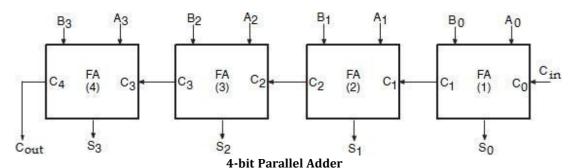

The 4-bit binary adder using full adder circuits is capable of adding two 4-bit numbers resulting in a 4-bit sum and a carry output as shown in figure below.

4-bit binary parallel Adder

Since all the bits of augend and addend are fed into the adder circuits simultaneously and the additions in each position are taking place at the same time, this circuit is known as parallel adder.

Let the 4-bit words to be added be represented by,

$A_3A_2A_1A_0 = 1111$  and  $B_3B_2B_1B_0 = 0011$ .

Significant place 4 3 2 1

Input carry 1 1 1 0

Augend word A: 1 1 1 1

Addend word B: 0 0 1 1

1 0 0 1 0 ← Sum

↑

Output Carry

The bits are added with full adders, starting from the least significant position, to form the sum it and carry bit. The input carry  $C_0$  in the least significant position must be 0. The carry output of the lower order stage is connected to the carry input of the next higher order stage. Hence this type of adder is called ripple-carry adder.

In the least significant stage,  $A_0$ ,  $B_0$  and  $C_0$  (which is 0) are added resulting in sum  $S_0$  and carry  $C_1$ . This carry  $C_1$  becomes the carry input to the second stage. Similarly in the second stage,  $A_1$ ,  $B_1$  and  $C_1$  are added resulting in sum  $S_1$  and carry  $C_2$ , in the third stage,  $A_2$ ,  $B_2$  and  $C_2$  are added resulting in sum  $S_2$  and carry  $C_3$ , in the third stage,  $A_3$ ,  $B_3$  and  $C_3$  are added resulting in sum  $S_3$  and  $C_4$ , which is the output carry. Thus the circuit results in a sum  $(S_3S_2S_1S_0)$  and a carry output  $(C_{out})$ .

Though the parallel binary adder is said to generate its output immediately after the inputs are applied, its speed of operation is limited by the carry propagation delay

through all stages. However, there are several methods to reduce this delay.

One of the methods of speeding up this process is look-ahead carry addition which eliminates the ripple-carry delay.

### **Carry Propagation-Look-Ahead Carry Generator:**

In Parallel adder, all the bits of the augend and the addend are available for computation at the same time. The carry output of each full-adder stage is connected to the carry input of the next high-order stage. Since each bit of the sum output depends on the value of the input carry, time delay occurs in the addition process. This timedelay is called as **carry propagation delay**.

For example, addition of two numbers (0011+ 0101) gives the result as 1000. Addition of the LSB position produces a carry into the second position. This carry when added to the bits of the second position, produces a carry into the third position. This carry when added to bits of the third position, produces a carry into the last position. The sum bit generated in the last position (MSB) depends on the carry that was generated by the addition in the previous position. i.e., the adder will not produce correct result until LSB carry has propagated through the intermediate full-adders. This represents a time delay that depends on the propagation delay produced in an each full-adder. For example, if each full adder is considered to have a propagation delay of

30nsec, then  $S_3$  will not react its correct value until 90 nsec after LSB is generated. Therefore total time required to perform addition is 90 + 30 = 120nsec.

The method of speeding up this process by eliminating inter stage carry delay is called **look ahead-carry addition**. This method utilizes logic gates to look at the lower order bits of the augend and addend to see if a higher-order carry is to be generated. It uses two functions: carry generate and carry propagate.

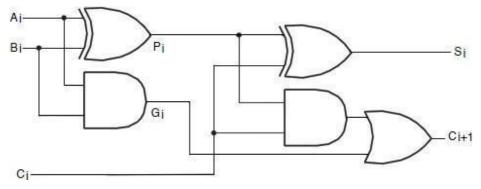

#### Full-Adder circuit

Consider the circuit of the full-adder shown above. Here we define two functions: carry generate (G<sub>i</sub>) and carry propagate (P<sub>i</sub>) as,

Carry generate,

$$G_i = A_i \square B_i$$

Carry propagate,

$$P_i = A_i \square B_i$$

the output sum and carry can be expressed as,

$$S_i = P_i \square C_i$$

$$C_{i+1} = G_i \square P_iC_i$$

G<sub>i</sub> (carry generate), it produces a carry 1 when both Ai and Bi are 1, regardless of the input carry C<sub>i</sub>.

Pi (carry propagate) because it is the term associated with the propagation of the carry from  $C_i$  to  $C_{i+1}$ .

The Boolean functions for the carry outputs of each stage and substitute for each C<sub>i</sub> its value from the previous equation:

C<sub>0</sub>= input carry

$$C_1 = G_0 + P_0C_0$$

$$C_2 = G_1 + P_1C_1 = G_1 + P_1 (G_0 + P_0C_0)$$

$$= G_1 + P_1G_0 + P_1P_0C_0$$

$$C_3 = G_2 + P_2C_2 = G_2 + P_2(G_1 + P_1G_0 + P_1P_0C_0)$$

=  $G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$

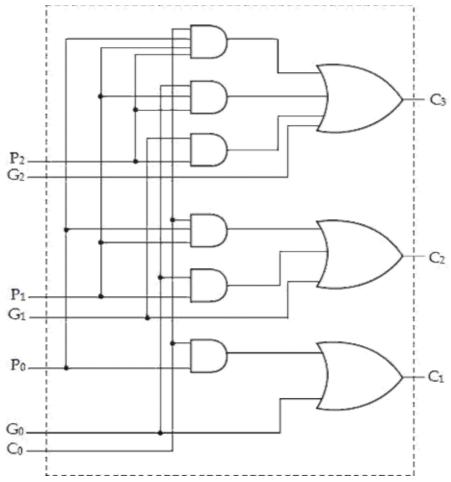

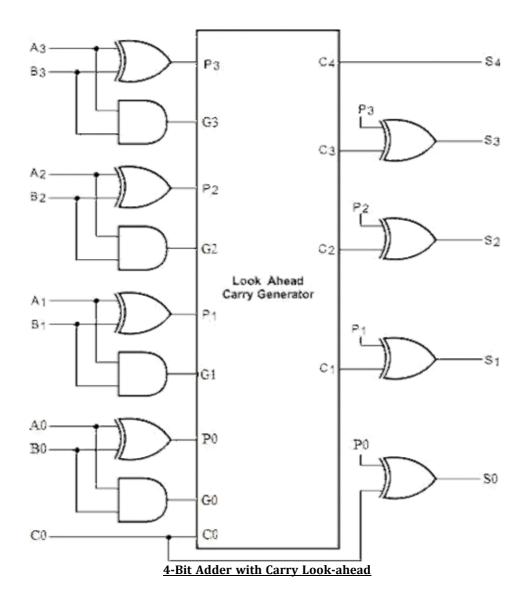

Since the Boolean function for each output carry is expressed in sum of products, each function can be implemented with one level of AND gates followed by an OR gate. The three Boolean functions for C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> are implemented in the carry look-ahead generator as shown below. Note that C<sub>3</sub> does not have to wait for C<sub>2</sub> and C<sub>1</sub> to propagate; in fact C<sub>3</sub> is propagated at the same time as C<sub>1</sub> and C<sub>2</sub>.

#### Logic diagram of Carry Look-ahead Generator

Using a Look-ahead Generator we can easily construct a 4-bit parallel adder with a Look-ahead carry scheme. Each sum output requires two exclusive-OR gates. The output of the first exclusive-OR gate generates the Pivariable, and the AND gate generates the Givariable. The carries are propagated through the carry look-ahead generator and applied as inputs to the second exclusive-OR gate. All output carries are generated after a delay through two levels of gates. Thus, outputs S1 through S3 have equal propagation delay times.

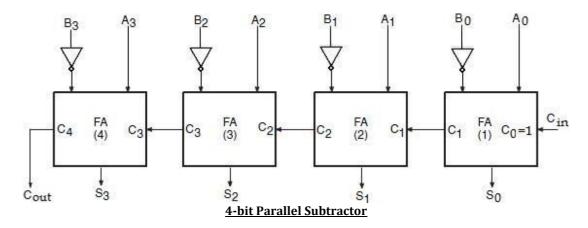

# **Binary Subtractor (Parallel Subtractor):**

The subtraction of unsigned binary numbers can be done most conveniently by means of complements. The subtraction A-B can be done by taking the 2's complement of B and adding it to A. The 2's complement can be obtained by taking the 1's complement and adding 1 to the least significant pair of bits. The 1's complement can be implemented with inverters and a 1 can be added to the sum through the input carry.

The circuit for subtracting A-B consists of an adder with inverters placed between each data input B and the corresponding input of the full adder. The input carry  $C_0$  must be equal to 1 when performing subtraction. The operation thus performed becomes A, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of B.

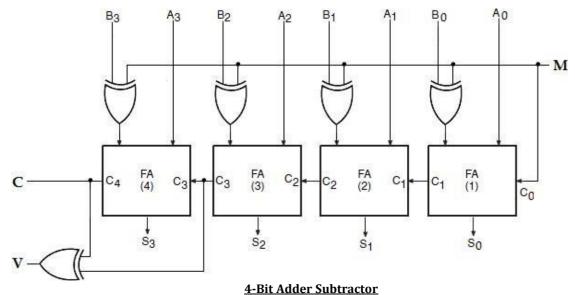

### Parallel Adder/ Subtractor:

The addition and subtraction operation can be combined into one circuit with one common binary adder. This is done by including an exclusive-OR gate with each full adder. A 4-bit adder Subtractor circuit is shown below.

The mode input M controls the operation. When M= 0, the circuit is an adder and when M=1, the circuit becomes a Subtractor. Each exclusive-OR gate receives input M

and one of the inputs of B. When M=0, we have B $\square$ 0 = B. The full adders receive the value of B, the input carry is 0, and the circuit performs A plus B. When M=1, we have B 1 $\equiv$  B' and C<sub>0</sub>=1. The B inputs are all complemented and a 1 is added through the input carry. The circuit performs the operation A plus the 2's complement of B. The exclusive-OR with output V is for detecting an overflow.

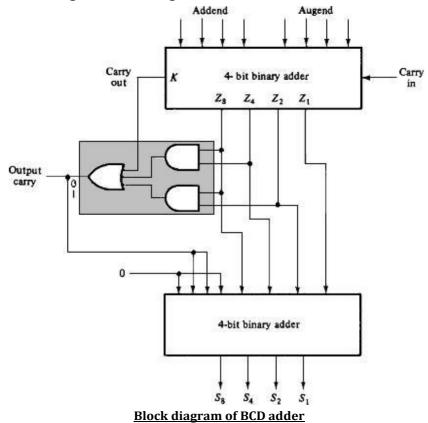

### Decimal Adder (BCD Adder):

The digital system handles the decimal number in the form of binary coded decimal numbers (BCD). A BCD adder is a circuit that adds two BCD bits and produces asum digit also in BCD.

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 9+9+1=19; the 1 is the sum being an input carry. The adder will form the sum in binary and produce a result that ranges from 0 through 19.

These binary numbers are labeled by symbols K, Z<sub>8</sub>, Z<sub>4</sub>, Z<sub>2</sub>, Z<sub>1</sub>, K is the carry. The columns under the binary sum list the binary values that appear in the outputs of the 4-bit binary adder. The output sum of the two decimal digits must be represented in BCD.

|   | Bina       | ary        | Sum                                         |   | BCD Sum |            |                |            |                |         |

|---|------------|------------|---------------------------------------------|---|---------|------------|----------------|------------|----------------|---------|

| К | <b>Z</b> 8 | <b>Z</b> 4 | <b>Z</b> <sub>2</sub> <b>Z</b> <sub>1</sub> |   | C       | <b>S</b> 8 | S <sub>4</sub> | <b>S</b> 2 | S <sub>1</sub> | Decimal |

| 0 | 0          | 0          | 0                                           | 0 | 0       | 0          | 0              | 0          | 0              | 0       |

| 0 | 0          | 0          | 0                                           | 1 | 0       | 0          | 0              | 0          | 1              | 1       |

| 0 | 0          | 0          | 1                                           | 0 | 0       | 0          | 0              | 1          | 0              | 2       |

| 0 | 0          | 0          | 1                                           | 1 | 0       | 0          | 0              | 1          | 1              | 3       |

| 0 | 0          | 1          | 0                                           | 0 | 0       | 0          | 1              | 0          | 0              | 4       |

| 0 | 0          | 1          | 0                                           | 1 | 0       | 0          | 1              | 0          | 1              | 5       |

| 0 | 0          | 1          | 1                                           | 0 | 0       | 0          | 1              | 1          | 0              | 6       |

| 0 | 0          | 1          | 1                                           | 1 | 0       | 0          | 1              | 1          | 1              | 7       |

| 0 | 1          | 0          | 0                                           | 0 | 0       | 1          | 0              | 0          | 0              | 8       |

| 0 | 1          | 0          | 0                                           | 1 | 0       | 1          | 0              | 0          | 1              | 9       |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 10 |

|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 11 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 12 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 13 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 14 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 15 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 16 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 17 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 18 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 19 |

In examining the contents of the table, it is apparent that when the binary sum is equal to or less than 1001, the corresponding BCD number is identical, and therefore no conversion is needed. When the binary sum is greater than 9 (1001), we obtain a non-valid BCD representation. The addition of binary 6 (0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

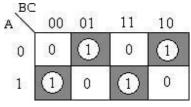

The logic circuit to detect sum greater than 9 can be determined by simplifying the boolean expression of the given truth table.

| Inputs                |                       |                       |                | Output |  |

|-----------------------|-----------------------|-----------------------|----------------|--------|--|

| <b>S</b> <sub>3</sub> | <b>S</b> <sub>2</sub> | <b>S</b> <sub>1</sub> | S <sub>0</sub> | Y      |  |

| 0                     | 0                     | 0                     | 0              | 0      |  |

| 0                     | 0                     | 0                     | 1              | 0      |  |

| 0                     | 0                     | 1                     | 0              | 0      |  |

| 0                     | 0                     | 1                     | 1              | 0      |  |

| 0                     | 1                     | 0                     | 0              | 0      |  |

| 0                     | 1                     | 0                     | 1              | 0      |  |

| 0                     | 1                     | 1                     | 0              | 0      |  |

| 0                     | 1                     | 1                     | 1              | 0      |  |

| 1                     | 0                     | 0                     | 0              | 0      |  |

| 1                     | 0                     | 0                     | 1              | 0      |  |

| 1                     | 0                     | 1                     | 0              | 1      |  |

| 1                     | 0                     | 1                     | 1              | 1      |  |

| 1                     | 1                     | 0                     | 0              | 1      |  |

| 1                     | 1                     | 0                     | 1              | 1      |  |

| 1                     | 1                     | 1                     | 0              | 1      |  |

| 1                     | 1                     | 1                     | 1              | 1      |  |

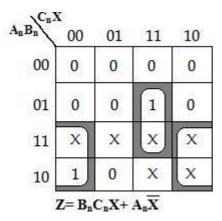

| S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> | S <sub>0</sub> | 01 | 11 | 10 |

|----------------------------------------------|----------------|----|----|----|

| 00                                           | 0              | 0  | 0  | 0  |

| 01                                           | 0              | 0  | 0  | 0  |

| 11                                           | 1              | 1  | 1  | 1  |

| 10                                           | 0              | 0  | 1  | 1  |

$Y = S_3S_2 + S_3S_1$

To implement BCD adder we require:

- 4-bit binary adder for initial addition

- Logic circuit to detect sum greater than 9 and

- One more 4-bit adder to add 01102 in the sum if the sum is greater than 9 or carry is 1.

The two decimal digits, together with the input carry, are first added in the top4-bit binary adder to provide the binary sum. When the output carry is equal to zero, nothing is added to the binary sum. When it is equal to one, binary 0110 is added to the binary sum through the bottom 4-bit adder. The output carry generated from the bottom adder can be ignored, since it supplies information already available at the output carry terminal. The output carry from one stage must be connected to the input carry of the next higher-order stage.

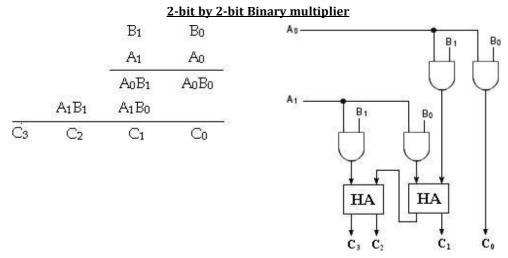

### **Binary Multiplier:**

Multiplication of binary numbers is performed in the same way as in decimal numbers. The multiplicand is multiplied by each bit of the multiplier starting from the least significant bit. Each such multiplication forms a partial product. Such partial

products are shifted one position to the left. The final product is obtained from the sum of partial products.

Consider the multiplication of two 2-bit numbers. The multiplicand bits are  $B_1$  and  $B_0$ , the multiplier bits are  $A_1$  and  $A_0$ , and the product is  $C_3$ ,  $C_2$ ,  $C_1$  and  $C_0$ . The first partial product is formed by multiplying  $A_0$  by  $B_1B_0$ . The multiplication of two bits such as  $A_0$  and  $B_0$  produces a 1 if both bits are 1; otherwise, it produces a 0. This is identical an AND operation. Therefore the partial product can be implemented with ANDgates as shown in the diagram below.

The second partial product is formed by multiplying  $A_1$  by  $B_1B_0$  and shifted one position to the left. The two partial products are added with two half adder (HA) circuits.

Usually there are more bits in the partial products and it is necessary to use full adders to produce the sum of the partial products. The least significant bit of the product does not have to go through an adder since it is formed by the output of thefirst AND gate.

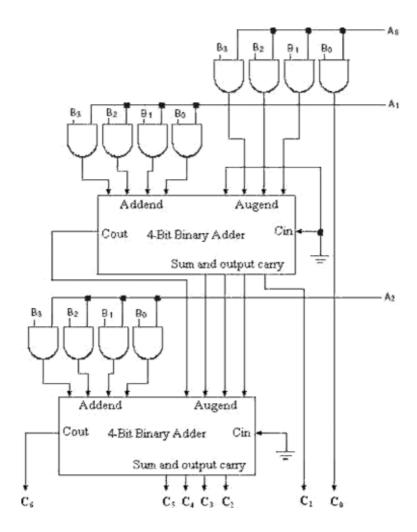

A combinational circuit binary multiplier with more bits can be constructed in a similar fashion. A bit of the multiplier is ANDed with each bit of the multiplicand in as many levels as there are bits in the multiplier. The binary output in each level of AND gates are added with the partial product of the previous level to form a new partial product. The last level produces the product. For J multiplier bits and K multiplicand bits we need ( $J \times K$ ) AND gates and ( $J \times K$ ) and  $J \times K$  bits.

Consider a multiplier circuit that multiplies a binary number of four bits by a number of three bits. Let the multiplicand be represented by B3, B2, B1, B0 and the multiplier by A2, A1, and A0. Since K= 4 and J= 3, we need 12 AND gates and two 4-bit adders to produce a product of seven bits. The logic diagram of the multiplier is shown below.

4-bit by 3-bit Binary multiplier

### PARITY GENERATOR/ CHECKER:

A *Parity* is a very useful tool in information processing in digital computers to indicate any presence of error in bit information. External noise and loss of signal strength causes loss of data bit information while transporting data from one device to other device, located inside the computer or externally. To indicate any occurrence of error, an extra bit is included with the message according to the total number of 1s in a set of data, which is called *parity*.

If the extra bit is considered 0 if the total number of 1s is even and 1 for odd quantities of 1s in a set of data, then it is called *even parity*. On the other hand, if the extra bit is 1 for even quantities of 1s and 0 for an odd number of 1s, then it is called *oddparity*.

The message including the parity is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker.

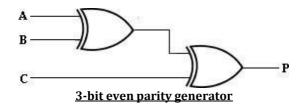

### **Parity Generator:**

A parity generator is a combination logic system to generate the parity bit at the transmitting side. A table illustrates even parity as well as odd parity for a message consisting of three bits.

| 3-bit Message |   |   | Odd Party | Even Parity |

|---------------|---|---|-----------|-------------|

| A             | В | С | bit       | bit         |

| 0             | 0 | 0 | 1         | 0           |

| 0             | 0 | 1 | 0         | 1           |

| 0             | 1 | 0 | 0         | 1           |

| 0             | 1 | 1 | 1         | 0           |

| 1             | 0 | 0 | 0         | 1           |

| 1             | 0 | 1 | 1         | 0           |

| 1             | 1 | 0 | 1         | 0           |

| 1             | 1 | 1 | 0         | 1           |

Parity generator truth table for even and odd parity

If the message bit combination is designated as A, B, C and  $P_e$ ,  $P_o$  are the even and odd parity respectively, then it is obvious from table that the boolean expressions of even parity and odd parity are

$$P_e = A \square (B \square C)$$

and

$$P_0 = (A \square B \square C)'.$$

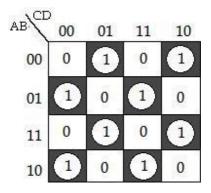

# **K-map Simplification:**

$$P = A'B'C + A'BC' + A'B'C' + ABC$$

$$= A' (B'C+BC') + A (B'C'+BC)$$

$$= A' (B \square C) + A (B \square C)'$$

$$=A\Box(B\Box C)$$

# **Logic Diagram:**

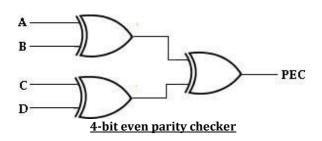

# **Parity Checker:**

The message bits with the parity bit are transmitted to their destination, where they are applied to a parity checker circuit. The circuit that checks the parity at the receiver side is called the *parity checker*. The parity checker circuit produces a check bit and is very similar to the parity generator circuit. If the check bit is 1, then it is assumed that the received data is incorrect. The check bit will be 0 if the received data is correct. The table shows the truth table for the even parity checker.

|   | 4-Bit R | Parity Error |   |             |

|---|---------|--------------|---|-------------|

| A | В       | С            | D | Check (PEC) |

| 0 | 0       | 0            | 0 | 0           |

| 0 | 0       | 0            | 1 | 1           |

| 0 | 0       | 1            | 0 | 1           |

| 0 | 0       | 1            | 1 | 0           |

| 0 | 1       | 0            | 0 | 1           |

| 0 | 1       | 0            | 1 | 0           |

| 0 | 1       | 1            | 0 | 0           |

| 0 | 1       | 1            | 1 | 1           |

| 1 | 0       | 0            | 0 | 1           |

| 1 | 0       | 0            | 1 | 0           |

| 1 | 0       | 1            | 0 | 0           |

| 1 | 0       | 1            | 1 | 1           |

| 1 | 1       | 0            | 0 | 0           |

| 1 | 1       | 0            | 1 | 1           |

| 1 | 1       | 1            | 0 | 1           |

| 1 | 1       | 1            | 1 | 0           |

# K-map Simplification:

### Logic Diagram:

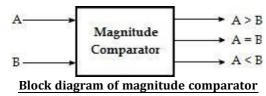

### MAGNITUDE COMPARATOR:

A *magnitude comparator* is a combinational circuit that compares two given numbers (A and B) and determines whether one is equal to, less than or greater than the other. The output is in the form of three binary variables representing the conditions A = B, A>B and A<B, if A and B are the two numbers being compared.

For comparison of two n-bit numbers, the classical method to achieve the Boolean expressions requires a truth table of  $2^{2n}$  entries and becomes too lengthy and cumbersome.

# **2-bit Magnitude Comparator:**

The truth table of 2-bit comparator is given in table below—

# Truth table:

| Inputs     |            |            |    | Outputs |     |                   |

|------------|------------|------------|----|---------|-----|-------------------|

| <b>A</b> 3 | <b>A</b> 2 | <b>A</b> 1 | Ao | A>B     | A=B | A <b< th=""></b<> |

| 0          | 0          | 0          | 0  | 0       | 1   | 0                 |

| 0          | 0          | 0          | 1  | 0       | 0   | 1                 |

| 0          | 0          | 1          | 0  | 0       | 0   | 1                 |

| 0          | 0          | 1          | 1  | 0       | 0   | 1                 |

| 0          | 1          | 0          | 0  | 1       | 0   | 0                 |

| 0          | 1          | 0          | 1  | 0       | 1   | 0                 |

| 0          | 1          | 1          | 0  | 0       | 0   | 1                 |

| 0          | 1          | 1          | 1  | 0       | 0   | 1                 |

| 1          | 0          | 0          | 0  | 1       | 0   | 0                 |

| 1          | 0          | 0          | 1  | 1       | 0   | 0                 |

| 1          | 0          | 1          | 0  | 0       | 1   | 0                 |

| 1          | 0          | 1          | 1  | 0       | 0   | 1                 |

| 1          | 1          | 0          | 0  | 1       | 0   | 0                 |

| 1          | 1          | 0          | 1  | 1       | 0   | 0                 |

| 1          | 1          | 1          | 0  | 1       | 0   | 0                 |

| 1          | 1          | 1          | 1  | 0       | 1   | 0                 |

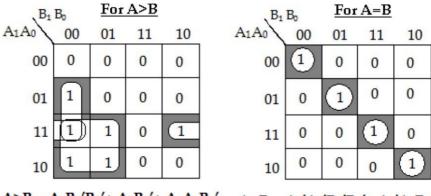

K-map Simplification:

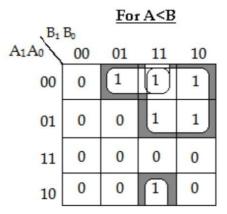

$$\begin{array}{ll} A > B = A_0 B_1' B_0' + A_1 B_1' + A_1 A_0 B_0' & A = B = A_1' A_0' B_1' B_0' + A_1' A_0 B_1' B_0 + \\ & A_1 A_0 B_1 B_0 + A_1 A_0' B_1 B_0' \\ & = A_1' B_1' \left( A_0' B_0' + A_0 B_0 \right) + A_1 B_1 \left( A_0 B_0 + A_0' B_0' \right) \\ & = \left( A_0 \odot B_0 \right) \left( A_1 \odot B_1 \right) \end{array}$$

$A < B = A_1'A_0'B_0 + A_0'B_1B_0 + A_1'B_1$

# **Logic Diagram:**

2- bit Magnitude Comparator

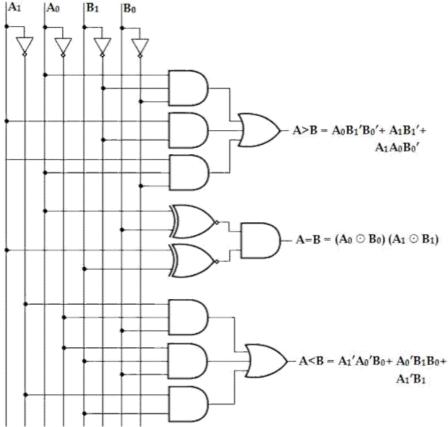

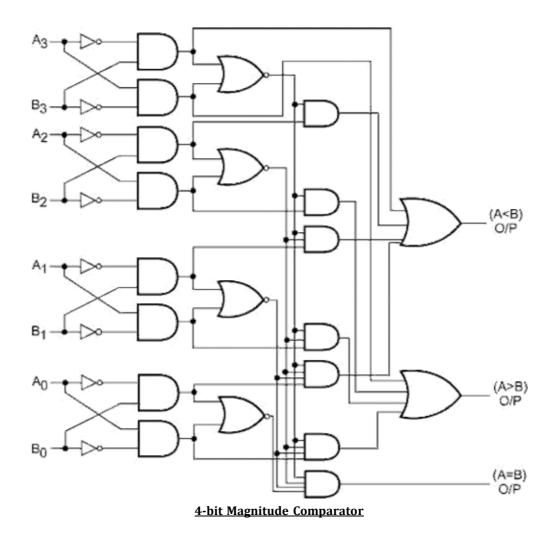

### **4-bit Magnitude Comparator:**

Let us consider the two binary numbers A and B with four digits each. Write the coefficient of the numbers in descending order as,

$$A = A_3A_2A_1A_0$$

$B = B_3 B_2 B_1 B_0$

Each subscripted letter represents one of the digits in the number. It is observed from the bit contents of two numbers that A = B when  $A_3 = B_3$ ,  $A_2 = B_2$ ,  $A_1 = B_1$  and  $A_0 = B_0$ . When the numbers are binary they possess the value of either 1 or 0, the equality relation of each pair can be expressed logically by the equivalence function as

$$Xi = AiBi + Ai'Bi'$$

for  $i = 1, 2, 3, 4$ .

Or,  $Xi = (A \square B)'$ . or,  $Xi' = A \square B$

Or,  $Xi = (AiBi' + Ai'Bi)'$ .

where,

Xi = 1 only if the pair of bits in position i are equal (ie., if both are 1 or both are 0).

To satisfy the equality condition of two numbers A and B, it is necessary that all Xi must be equal to logic 1. This indicates the AND operation of all Xi variables. In other words, we can write the Boolean expression for two equal 4-bit numbers.

$$(A = B) = X_3X_2X_1 X_0.$$

The binary variable (A=B) is equal to 1 only if all pairs of digits of the two numbers are equal.

To determine if A is greater than or less than B, we inspect the relative magnitudes of pairs of significant bits starting from the most significant bit. If the two digits of the most significant position are equal, the next significant pair of digits is compared. The comparison process is continued until a pair of unequal digits is found. It may be concluded that A>B, if the corresponding digit of A is 1 and B is 0. If the corresponding digit of A is 0 and B is 1, we conclude that A<B. Therefore, we can derive the logical expression of such sequential comparison by the following two Boolean functions,

$$(A>B) = A_3B_3' + X_3A_2B_2' + X_3X_2A_1B_1' + X_3X_2X_1A_0B_0'$$

$(A$

The symbols (A>B) and (A<B) are binary output variables that are equal to 1 when A>B or A<B, respectively.

The gate implementation of the three output variables just derived is simpler than it seems because it involves a certain amount of repetition. The unequal outputs can use the same gates that are needed to generate the equal output. The logic diagram of the 4-bit magnitude comparator is shown below,

The four x outputs are generated with exclusive-NOR circuits and applied to an AND gate to give the binary output variable (A=B). The other two outputs use the x variables to generate the Boolean functions listed above. This is a multilevel implementation and has a regular pattern.

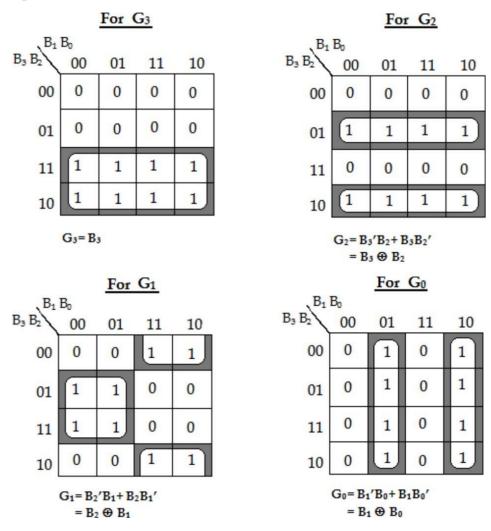

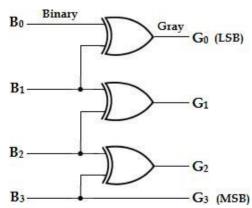

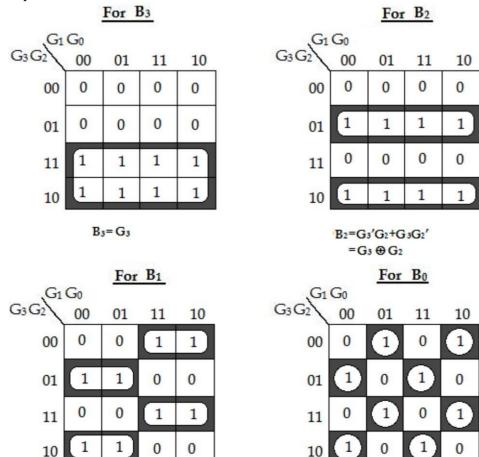

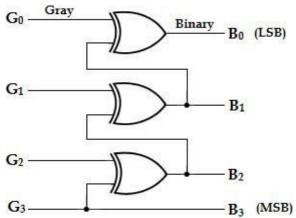

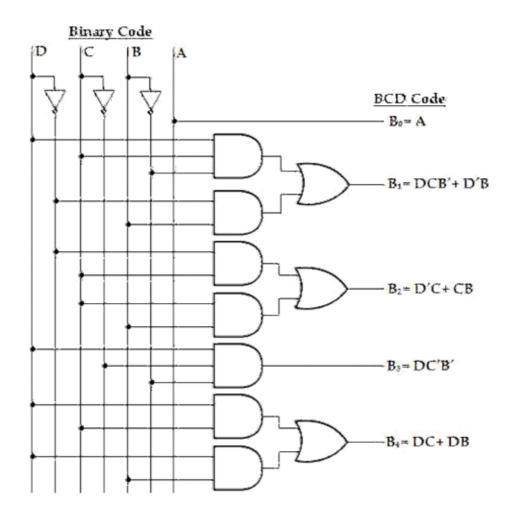

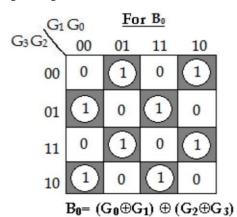

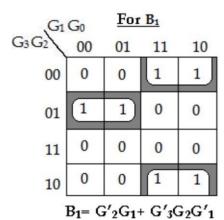

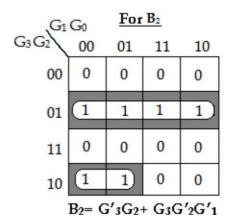

### **CODE CONVERTERS:**

A code converter is a logic circuit that changes data presented in one type of binary code to another code of binary code. The following are some of the most commonly used code converters:

- i. Binary-to-Gray code

- ii. Gray-to-Binary code

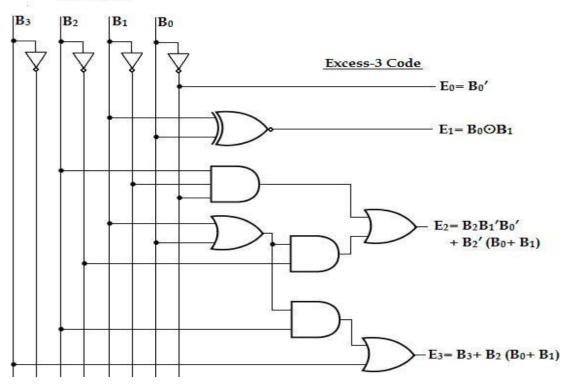

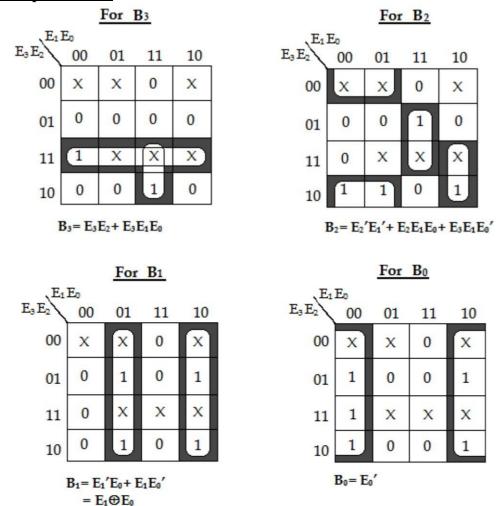

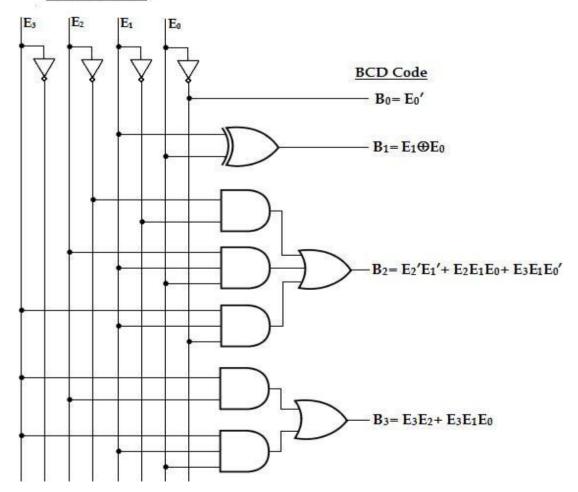

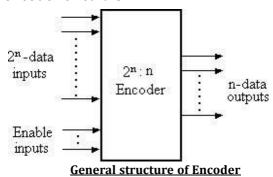

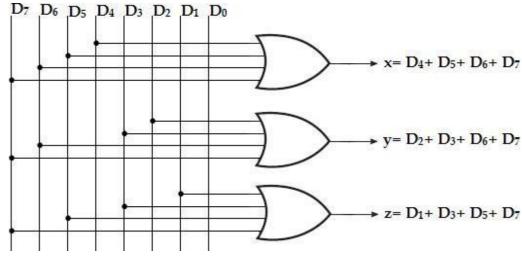

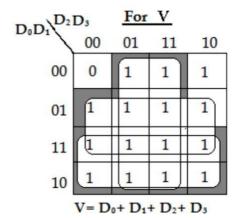

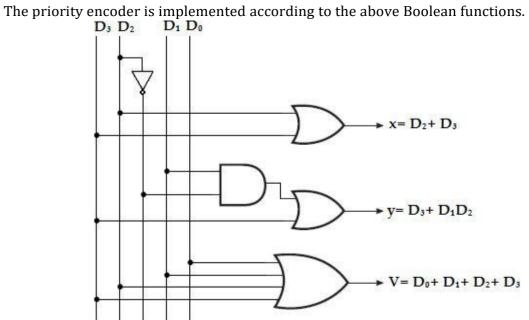

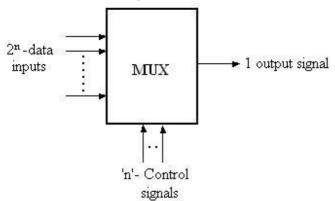

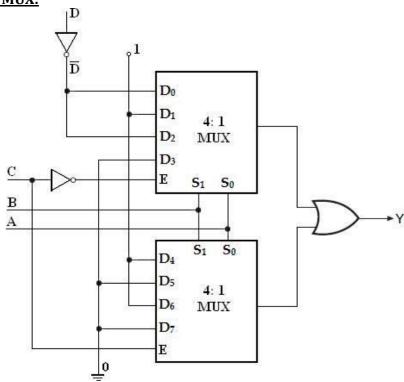

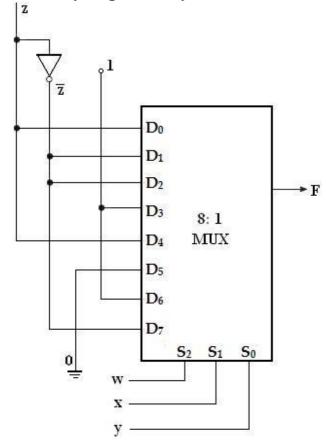

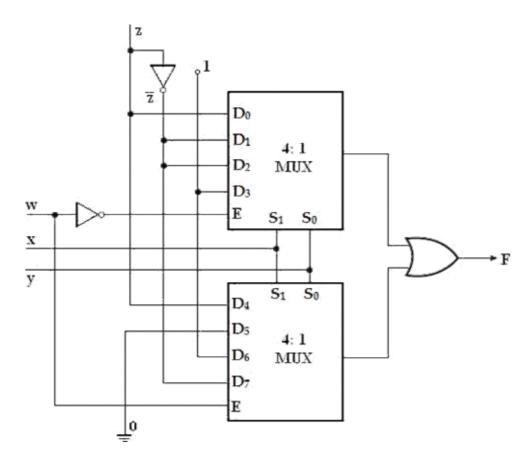

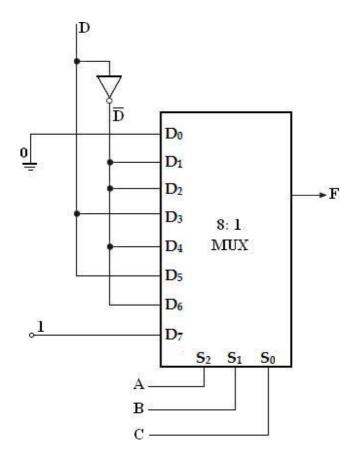

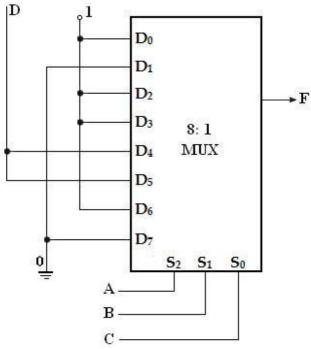

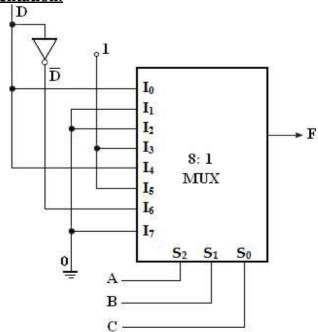

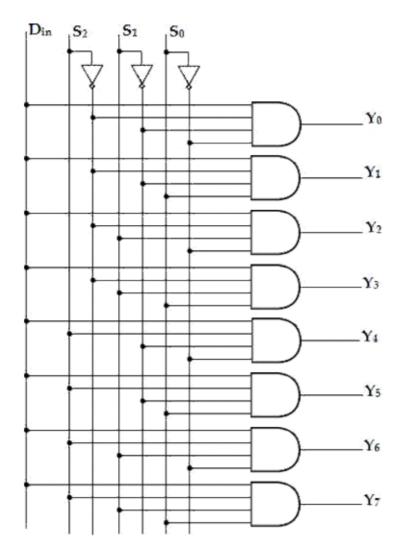

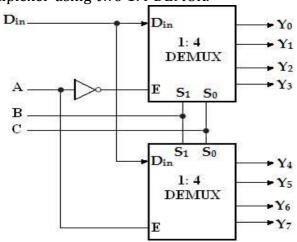

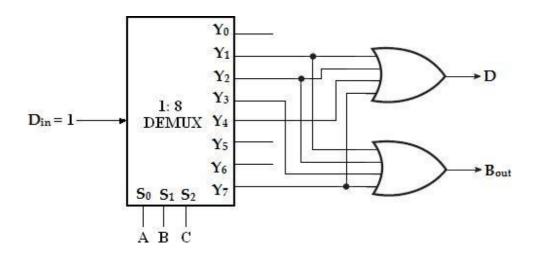

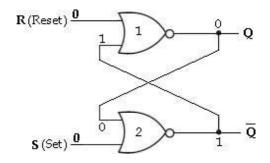

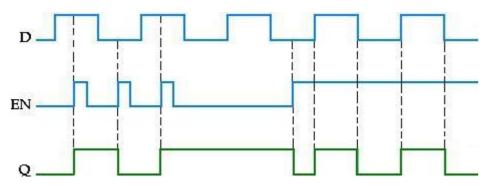

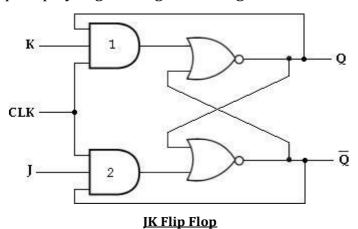

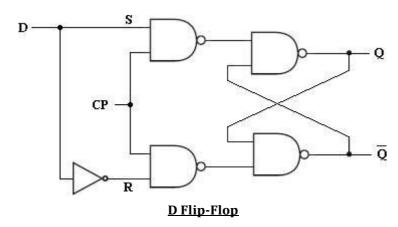

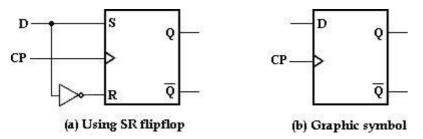

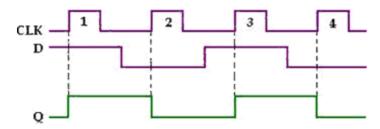

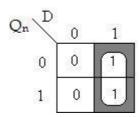

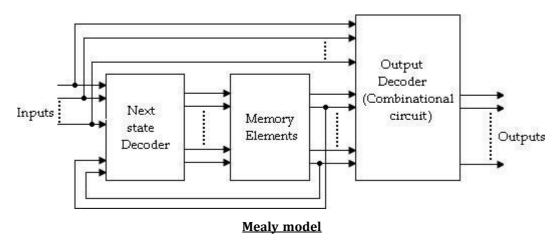

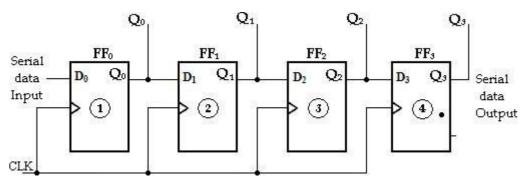

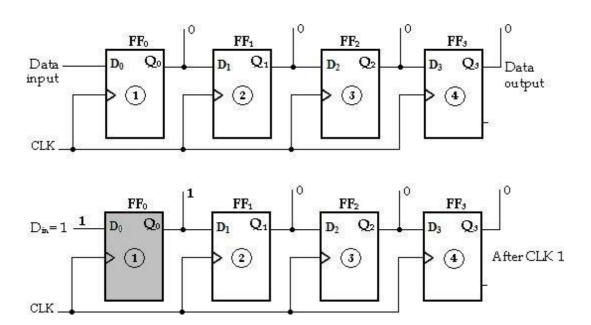

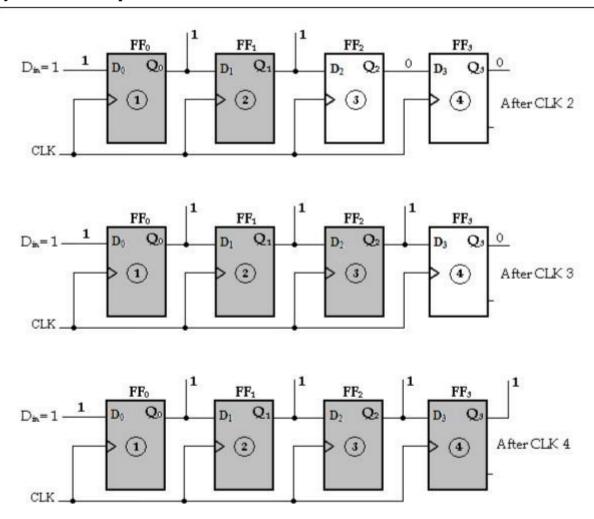

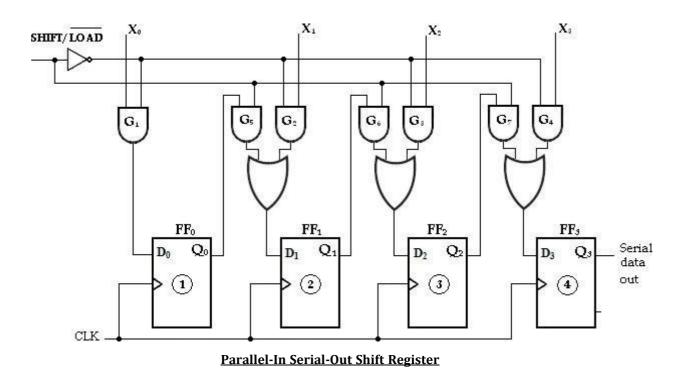

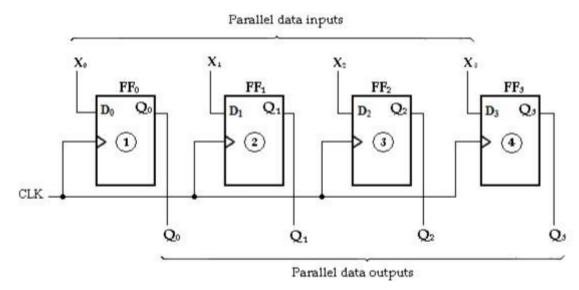

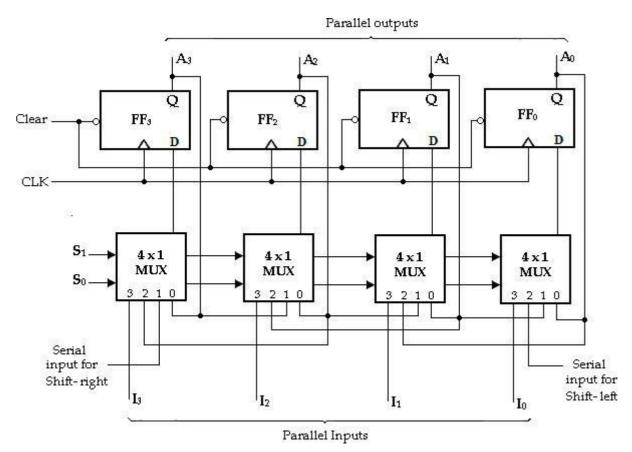

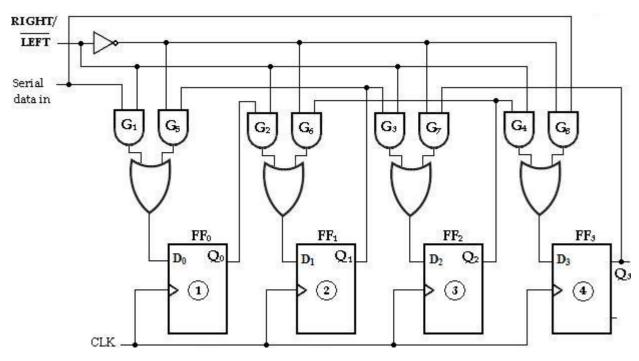

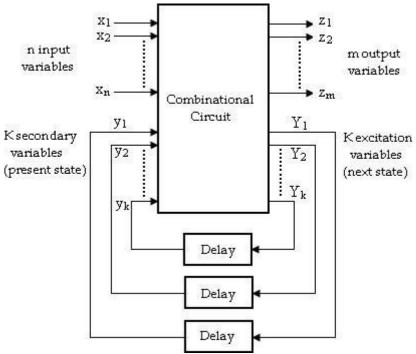

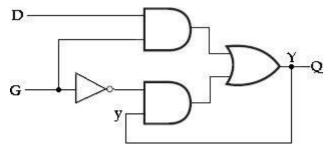

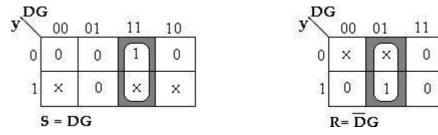

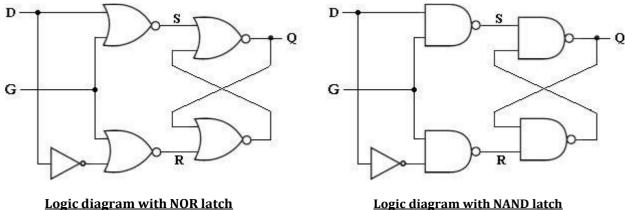

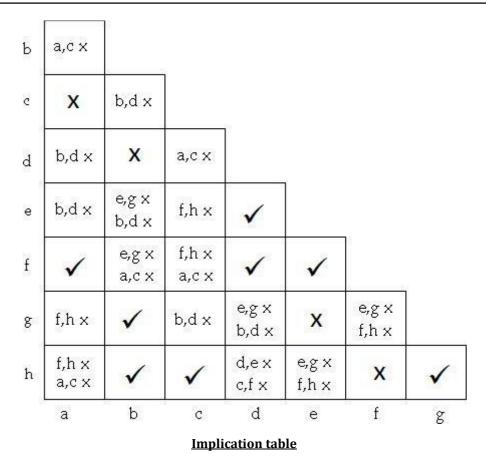

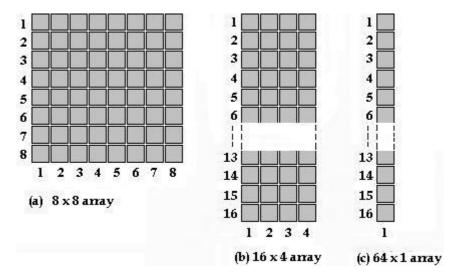

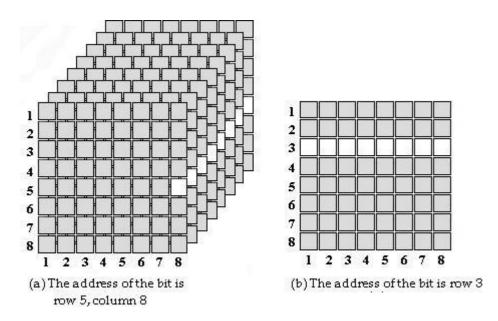

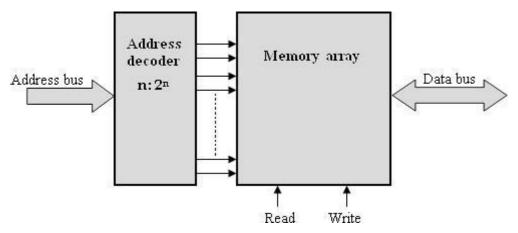

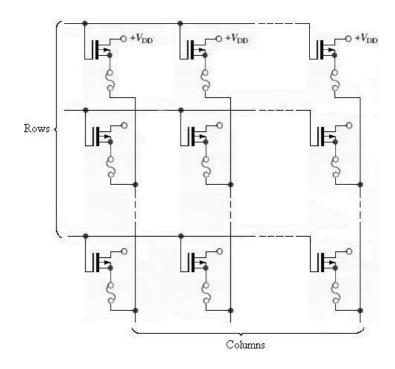

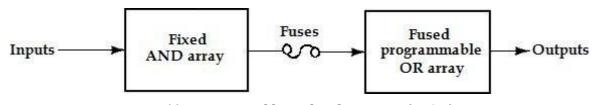

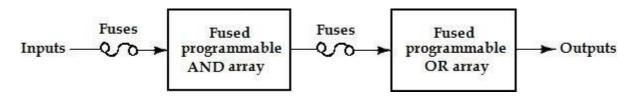

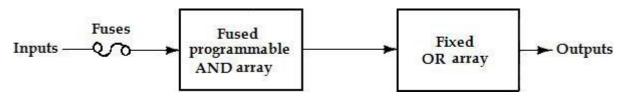

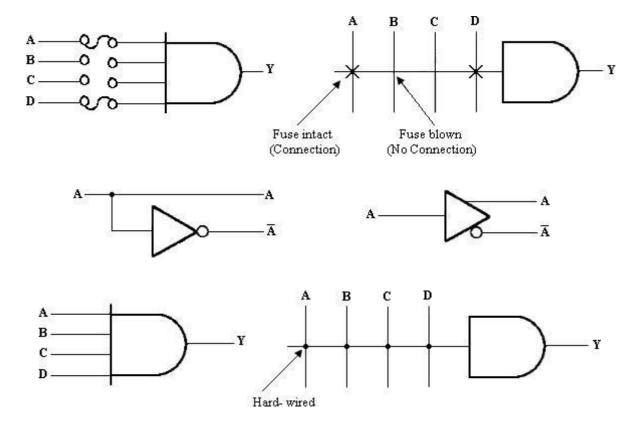

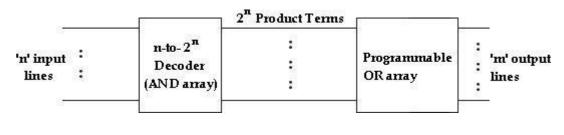

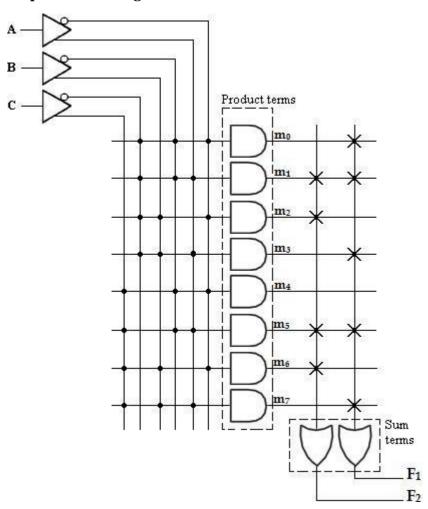

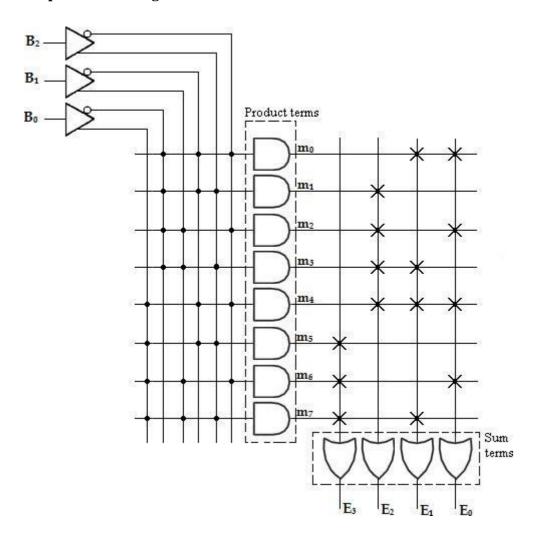

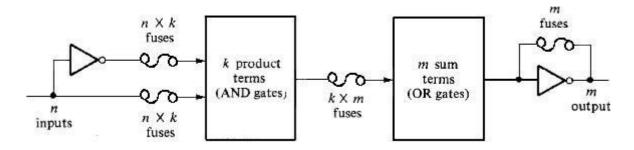

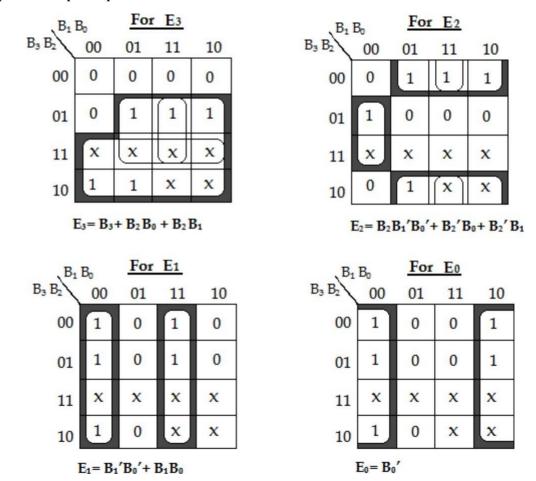

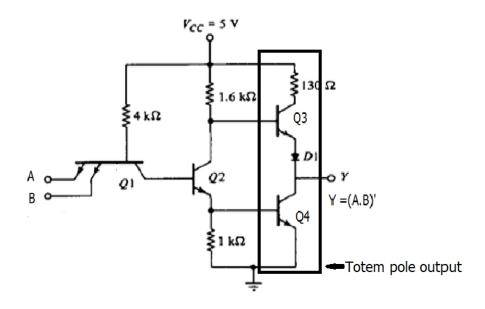

- iii. BCD-to-Excess-3